# TEXAS ANALOG CENTER OF EXCELLENCE

ERIK JONSSON SCHOOL OF ENGINEERING AND COMPUTER SCIENCE

# Annual Report 2019 – 2020

# **TXACE MISSION**

The Texas Analog Center of Excellence seeks to create fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

# **TXACE THRUSTS**

✓ Safety, Security and Health Care

✓ Energy Efficiency

✓ Fundamental Analog Circuits

# TxACE 2019–2020 ANNUAL REPORT

The Texas Analog Center of Excellence (TxACE), located at the University of Texas at Dallas is the largest analog research center based in an academic institution. Analog and mixed signal integrated circuits engineering is both a major opportunity and challenge. Analog circuitry is a critical component of the majority of products for the \$400+ billion per year integrated circuits industry, as a part of sensing, actuation, communication, power management and others. Digital integrated circuits such as microprocessors, logic circuits and memories are now integrating analog functions such as input/output circuits, phase locked loops, temperature sensors and power management circuits. It is also common to find microcontrollers with multiple analog-to-digital and digital-to-analog converters. These circuitries impact almost all aspect of modern life: safety security, health care, transportation, energy, entertainment and others.

Creation of advanced analog and mixed signal circuits and systems depends on the availability of engineering talent for analog research and development. TxACE was established to help translate the opportunity into economic benefits by overcoming the challenge and meeting the need. TxACE was established through a collaboration of the state of Texas, Texas Instruments, the Semiconductor Research Corporation, the University of Texas System, and The University of Texas at Dallas.

The research tasks are organized into three research thrust areas: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog. The scope of investigation extends from circuits operating at dc through terahertz, data converters that sample at a few samples/sec to 10's of Giga-samples/sec, AC-to-DC and DC-to-AC converters working at  $\mu$ W to Watts, energy harvesting circuits, sensors and many more. Significant improvements to existing mixed signal systems and new applications have been made and continued to be anticipated. Students who have been exposed to hands-on innovative research are forming the leading edge of analog talent flow into the industry. Close collaboration with and responsiveness to industry needs provide focus to the educational experience.

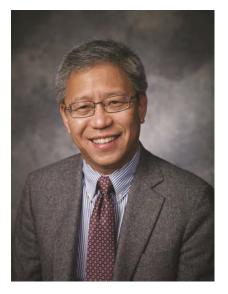

#### DIRECTOR'S MESSAGE

The Texas Analog Center of Excellence (TxACE) is leading analog research and education. During this year of COVID-19, it has become evident how important the efforts of the Center are. Can you imagine, what our life would have been like, if the pandemic happened 10 years ago? The technologies that the center has helped to create have become the necessary means for saving the civilization during this time. We are privileged to be able to contribute toward this.

It is my pleasure to report that the Center despite the disruption is making excellent progress toward accomplishing our mission. The Center funded 74 research tasks led by 63 principal investigators at 31 institutions, including four international universities. The Center supported 203 graduate and undergraduate students.

Over the past year, TxACE researchers published 29 journal and 48 conference papers. We also filed 5 patent applications and 2 invention disclosures, and were granted 2 patents. Twenty-three Ph.D., five M.S. and one B.S. students have completed their degree program.

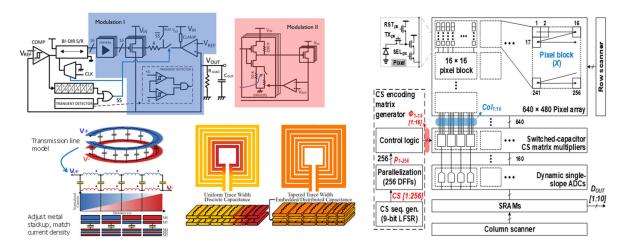

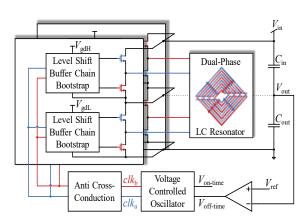

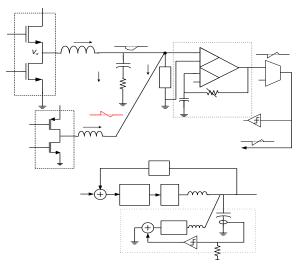

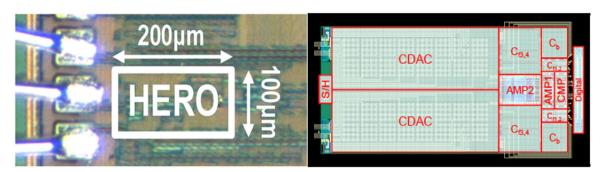

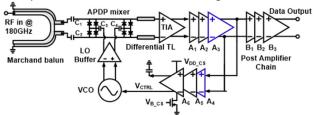

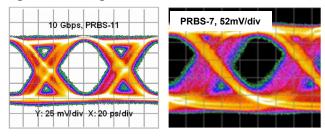

There are always too many research accomplishments to list all here. A selected list includes improving energy efficiency of CMOS imagers by >20x by employing a compressive sensing coding scheme utilizing a mixed-signal switched capacitor matrix multiplier, demonstrating that selecting ESD protection devices based on an eye diagram analysis reduces circuit performance degradation, improving energy density by 2x using a hybrid resonant switched capacitor converter with an integrated LC resonator while increasing efficiency, and demonstration of a 10-Gbps 315 GHz MSK receiver with 5X higher data rate than that for the state of art at 5X higher carrier frequency.

The TxACE laboratory is continuing to help advance integrated circuit research by making its instruments and expertise available to researchers and our industrial partners all over the world.

I would like to thank the students, principal investigators and staff for their efforts, and UT Dallas, the University of Texas System, TI, and SRC, as well as many friends of TxACE all over the world for their generous support. I look forward to another year of working with the TxACE team to make our way of life better, safer and healthier through our research, education and innovation.

Most importantly, I wish everybody health and safety.

Kenneth K. O, Director TxACE Texas Instruments Distinguished University Chair Professor The University of Texas at Dallas

#### **BACKGROUND & VISION**

The \$400+ billion per year integrated circuits industry is evolving into an analog/digital mixed signal industry. Analog circuits are providing or supporting critical functions such as sensing, actuation, communication, power management and others. These circuits impact almost all aspect of modern life including safety, security, health care, transportation, energy, and entertainment. To lead this change, in particular to lead analog and mixed signal technology education, research, commercialization, manufacturing, and job creation, the Texas Analog Center of Excellence was announced by Texas Governor Rick Perry in October 2008 as a collaboration of the Semiconductor Research Corporation, state of Texas through its Texas Emerging Technology Fund, Texas Instruments Inc., University of Texas system and University of Texas at Dallas. The Center seeks to accomplish the objectives by creating fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, healthcare, and public safety and security as well as by improving the research and educational infrastructure.

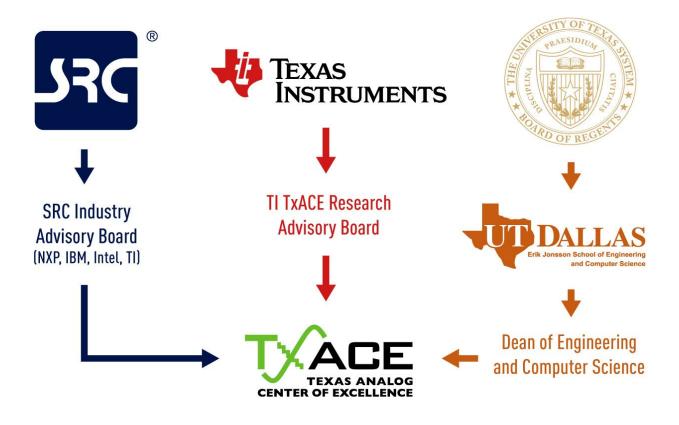

Figure 1. TxACE organization relative to the sponsoring collaboration (2019-2020).

#### **CENTER ORGANIZATION**

The Texas Analog Center of Excellence is guided by agreements established with the Center sponsors. Members of the industrial advisory boards identify the research needs and select research tasks in consultation with the Center leadership. Figure 1 diagrams the relationship of TxACE to the members of the sponsoring collaboration.

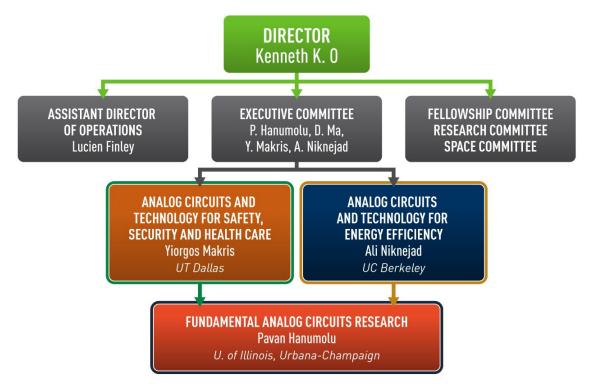

# The internal organization of the Center is structured to flexibly perform the research mission while fully embracing the educational missions of the Universities.

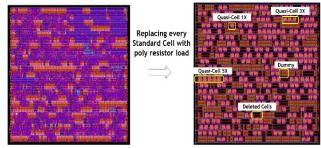

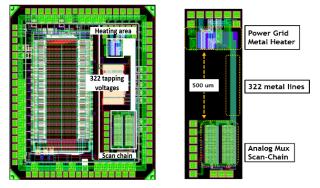

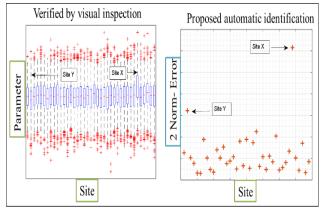

Figure 2 shows the center management structure. The TxACE Director is Professor Kenneth O. The research is arranged into three thrusts that comply with the center mission: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog Research. The third thrust consists of vital research that cuts across the first two research thrusts. The thrust leaders are Prof. Yiorgos Makris of the University of Texas at Dallas for safety, security and health care, and Prof. Ali Niknejad of the University of California, Berkeley for energy efficiency. The leader for fundamental analog is Prof. Pavan Hanumolu of University of Illinois, Urbana-Champaign. The thrust leaders along with Professor Dongsheng Ma of the The University of Texas at Dallas form the executive committee. The committee, along with the director, forms the leadership team that works to improve the research productivity by increasing collaboration, better leveraging the diverse capabilities of principle investigators of the Center, and lowering research barriers. The leadership team also identifies new research opportunities for consideration by the Industrial Advisory Boards.

Figure 2. TxACE organization for management of research

#### SAFETY, SECURITY & HEALTH CARE

(Thrust leader: Yiorgos Makris, University of Texas at Dallas)

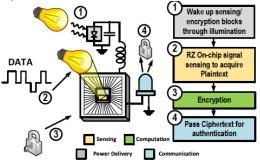

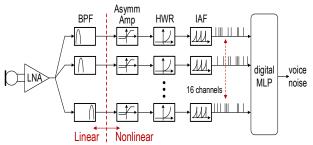

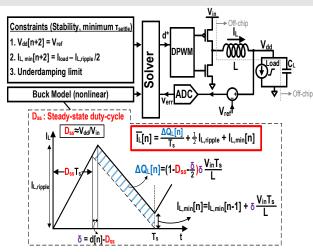

TxACE is developing analog technologies that enhance public safety and security, and health care. This thrust is working to improve safety by mitigating various reliability threats in analog/RF devices, including ESD, supply noise, temperature stress/strain and electro-migration, as well as by developing effective machine learning-based design, verification and self-test solutions. This thrust also seeks to reduce the cost of millimeter wave imaging and on-vehicle radar technology for automotive safety by researching signal processing techniques that reduce system complexity and transmitter architecture that can efficiently adapt to changing antenna characteristics, as well as sensor fusion techniques that can enable monitoring behaviors of a driver in an automobile. Furthermore, this thrust is investigating methods for remote attestation of IoT edge devices, security protocols for energy harvesting IoT nodes and security aware dynamic power management. Additionally, this thrust includes research towards designing efficient wearable IoT devices through 3D printing of distributed silicon circuits and sensors, as well as vital sign detection through millimeter wave radar.

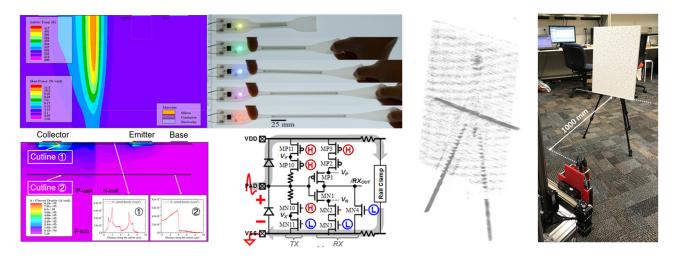

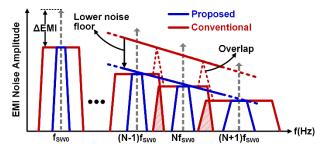

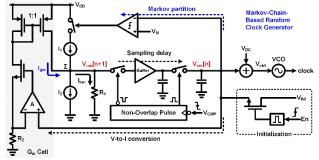

Figure 3. (Left) Holes current density distribution after parasitic substrate PNP triggers, with the current flow and crowding observable near the surface of the structure and the overall temperature distribution of the device @ I =300mA (Z. Chen, University of Arkansas), (Top center) Multi-layer printed LMP interconnects enable simple stretchable circuits using discrete components and embedded battery (M. Johnston & Y. Mengüc, Oregon State University), (Bottom center) Energy of the ESD pulse used to activate bias control circuitry that maximizes the transceiver robustness against the ESD-induced over-voltage stress at the IO pad (E. Rosenbaum, University of Illinois Urbana Champaign), (Right) Photograph of the small metal strip concealed behind a drywall located at a distance of 1000 mm, and reconstructed image in 3-D volumetric view (M. Torlak, UT Dallas).

(Thrust leader: Ali Niknejad, UC Berkeley)

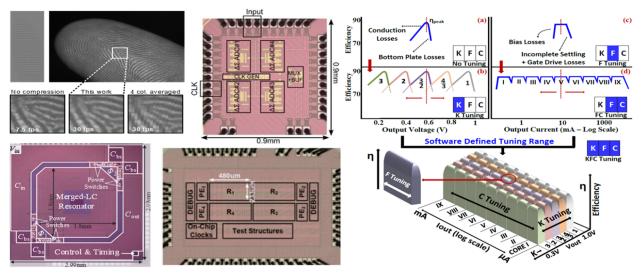

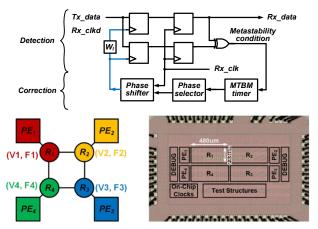

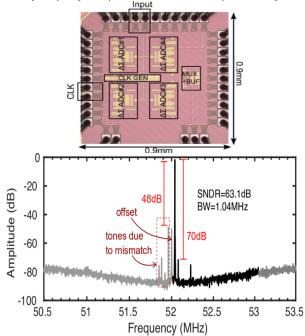

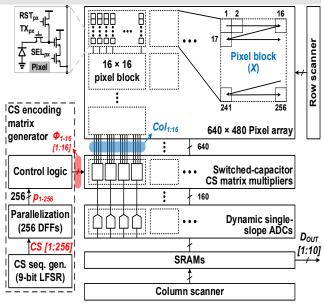

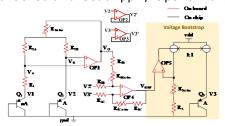

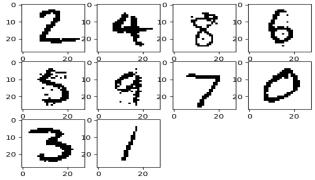

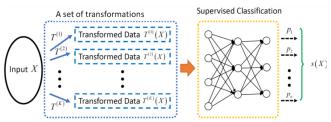

Figure 4. (Top left) Images captured using a compressive sensing coding scheme for a CMOS imager with a switched capacitor mixed-signal matrix multiplier improves the state-of-art energy efficiency by >20x. (N. Sun, UT Austin), (Top center) A VCO-based Bandpass-ADC by 4x time-interleaving our prior second-order LP-ADC that achieves a record-breaking band-pass Walden FoM of 57fJ/step. (A. Sanyal, U. of Buffalo), (Right) Efficiency profile of a capacitive converter and 3D-plot showing KFC (conversion ratio frequency capacitance) tuning for a direct battery-to-silicon DC-DC converter in CMOS using a multi-resonant coupled-inductor with 80% efficiency over a wide conversion range (0.2 - 0.8). (R. Harjani, U. of Minnesota), (Bottom left) Merged LC resonant switched capacitor for 2:1 step down with regulation @ 45 MHz. (J. Stauth, Dartmouth), (Bottom center) Metastability error detection and correction integrated circuit (MEDAC) consisting of 4 routers and PEs each having its own V/F domain (M. Seok, Columbia U.).

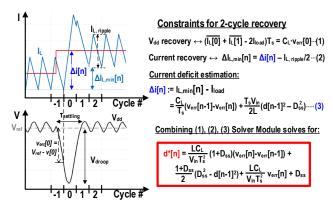

TxACE is committed to alleviate the global energy problem by improving the energy efficiency of electronic systems as well as by developing analog technologies that can make energy generation, distribution and utilization more efficient. The Center is also working to energize and power long-lasting in-situ microscale devices such as wireless microsensors, biomedical implants, and portable microelectronics. The research in this thrust includes power converters, co-optimization of converters and regulators with systems powered by them, I/O with power consumption that scales with the data rate, optimization of TSV placement for thermal management, efficient drivers for a power stage with reduced EMI, ultra low-power analog to digital converters, ultra-capacitors formed using carbon nano-tubes, a fast start-up crystal oscillator with reduced power consumption, built-in self-test for power management IC's, System-In-Package energy harvester and others. Many of the solutions employ mixed-signal techniques, exploiting digital trends and utilize novel scaling friendly analog architectures in order to improve the control and expand the flexibility of the overall system

### FUNDAMENTAL ANALOG CIRCUITS RESEARCH

(Thrust leader: Pavan Hanumolu, U. of Illinois Urbana-Champaign)

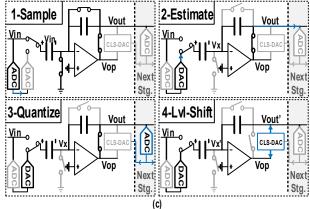

Research in this thrust focuses on cross-cutting areas in analog and mixed signal circuits which impact all of the TxACE application areas (Energy Efficiency, Public Safety and Security, Health Care). The list of research includes design of a wide variety of analog-to-digital converters, communication links, low-power crystal oscillators, I/O circuits, noise reduction techniques, new amplifier topologies suitable for use in nano-scale CMOS, development of CAD tools and testing of integrated circuits.

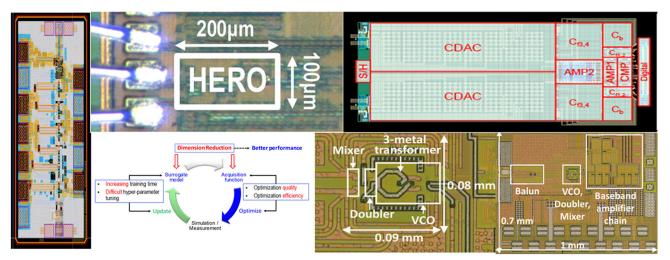

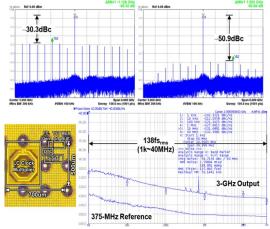

Figure 5. (Left) 170 - 260 GHz wideband LNA (A. Babakhani, UCLA), (Top cneter) Ultra-low-power crystal oscillator (D. Sylvester, University of Michigan), (Top right) Fourth-order noise shaping SAR ADC (M. Flynn, University of Michigan), (Bottom center) Bayesian optimization based rare failure detection for analog and mixed-signal circuits (P. Li, UC Santa Barbara), (Bottom right) 315 GHz minimum shift keying receiver (K. O, UT Dallas).

### **TXACE ANALOG RESEARCH FACILITY**

The centralized group of laboratories of the Texas Analog Center of Excellence dedicated to analog engineering research and training occupy a ~ 8000-ft2 area on the 3rd floor of the Engineering and Computer Science North building (Figure 6). The facility includes RF and THz, Integrated System Design, Embedded Signal Processing, and Analog & Mixed Signal laboratories as well as CAD/Design laboratory structured to promote collaborative research. The unique instrumentation capability includes network analyses and linearity measurements up to 325 GHz, spectrum analysis up to 120 THz, and cryo-measurements down to 2°K. The Center also added a pulsed multiple harmonic load and source pull measurement set up (up to 60 GHz for the third harmonic) and a 325-GHz antenna measurement set up. The close proximity of researchers in an open layout enables natural interaction and compels sharing of knowledge and instrumentation among the students and faculty. The TxACE analog research facility is one of the best equipped electronics laboratories. The laboratory is available for use by TxACE researchers and industrial partners all over the world.

Figure 6. TxACE Analog Research Facility

#### **RESEARCH PROJECTS AND INVESTIGATORS**

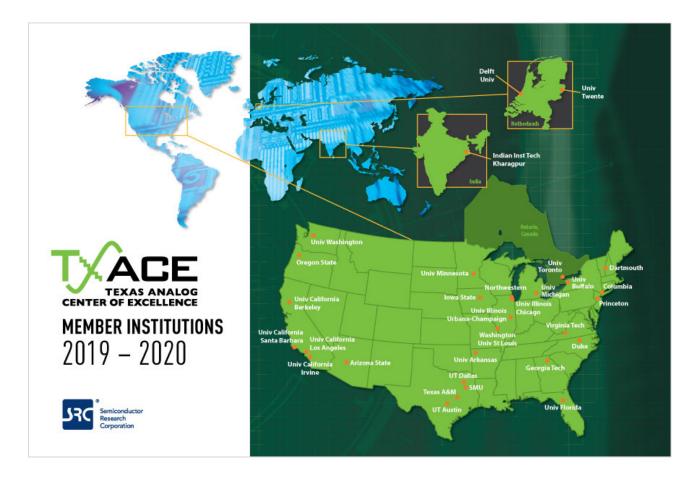

The Texas Analog Center of Excellence (TxACE) is the largest university analog technology center in the world. Table 1 lists the current principal investigators of the 74 tasks from 31 academic institutions funded by TxACE. Four universities (SMU, Texas A&M, UT Austin, UT Dallas) are from the state of Texas. Twenty-three are from outside of Texas. Four (Delft University of Technology, University of Twente, Indian Institute of Tech. Kharagpur, and University of Toronto) (Figure 7) are from outside of the US. Of the 63 investigators, 18 are from Texas. During the past year, the Center supported 168 Ph.D., 23 M.S., and 12 B.S. students. 23 Ph.D., five M.S., and one B.S. degrees were awarded to the TxACE students.

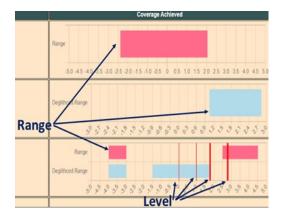

| Investigator   | Institution                         | Investigator    | Institution                            | Investigator   | Institution             |

|----------------|-------------------------------------|-----------------|----------------------------------------|----------------|-------------------------|

| B. Akin        | UT/Dallas A. Hazra                  |                 | Indian Institute of<br>Tech. Kharagpur | S. Ozev        | Arizona State           |

| N. Al-Dhahir   | UT/Dallas                           | R. Henderson    | UT/Dallas                              | S. Palermo     | TEES                    |

| A. Babakhani   | UCLA                                | S. Hoyos        | TEES                                   | S. Pamarti     | UCLA                    |

| N. Bagherzadeh | UC/Irvine                           | J. Hu           | TEES                                   | G. Rincon-Mora | Georgia Tech            |

| B. Bakkaloglu  | Arizona State                       | M. Johnston     | Oregon State U.                        | R. Rohrer      | SMU                     |

| S. Bhunia      | U. of Florida                       | C. Kim          | U. of Minnesota                        | E. Rosenbaum   | UIUC                    |

| D. Blaauw      | U. of Michigan                      | M. Kim          | UT/Dallas                              | A. Sanyal      | U. at Buffalo           |

| C. Busso       | UT/Dallas                           | G. Lee          | UT/Dallas                              | V. Sathe       | U. of Washington        |

| A. Chatterjee  | Georgia Tech                        | J. Lee          | UC/Irvine                              | P. Schaumont   | Virginia Tech           |

| D. Chen        | Iowa State U.                       | P. Li           | UC/Santa<br>Barbara                    | K. Sengupta    | Princeton               |

| Y. Chen        | Duke University                     | D. B. Ma        | UT/Dallas                              | M. Seok        | Columbia                |

| Z. Chen        | U. Arkansas/<br>Fayetteville        | N. Maghari      | U. of Florida                          | H. Shichijo    | UT/Dallas               |

| P. Dasgupta    | Indian Institute of Tech. Kharagpur | K. Makinwa      | Delft University                       | J. Stauth      | Dartmouth               |

| W. Eisenstadt  | U. of Florida                       | Y. Makris       | UT/Dallas                              | N. Sun         | UT/Austin               |

| M. Flynn       | U. of Michigan                      | Y. Menguc       | Oregon State U.                        | M. Swaminathan | Georgia Tech            |

| J. Friedman    | UT/Dallas                           | U. Moon         | Oregon State U.                        | D. Sylvester   | U. of Michigan          |

| R. Geiger      | Iowa State U.                       | S. Mukhopadhyay | Georgia Tech                           | G. Temes       | Oregon State U.         |

| J. Gu          | Northwestern U.                     | F. Najm         | U. of Toronto                          | S. Thompson    | U. of Florida           |

| P. Gui         | SMU                                 | B. Nauta        | U. of Twente                           | M. Torlak      | UT/Dallas               |

| P. Hanumolu    | UIUC                                | A. Niknejad     | UC/Berkeley                            | A. Trivedi     | U. Illinois,<br>Chicago |

| R. Harjani     | U. of Minnesota                     | К. О            | UT/Dallas                              | X. Zhang       | Washington U.           |

#### Table 1. Principal Investigators (May 2019 through April 2020)

Figure 7. Member Institutions of Texas Analog Center of Excellence

### SUMMARY OF RESEARCH PROJECTS

The 74 research projects funded through TxACE during 2019-2020 are listed in Table 2 below by the Semiconductor Research Corporation task identification number.

|    | Task     | Thrust | Title                                                                                                                                     | Task Leader              | Institution         |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------|

| 1  | 2712.002 | EE/SS  | On-line Self-Testing and Self-Tuning of Integrated<br>Voltage Regulators                                                                  | Mukhopadhyay,<br>Saibal  | Georgia Tech        |

| 2  | 2712.003 | SS     | Multi-Modal BIST Design and Test Metrics Evaluation<br>for Analog/RF Circuits                                                             | Ozev, Sule               | Arizona State       |

| 3  | 2712.005 | FA     | Automated Cross-Level Validation and Debug of<br>Mixed-Signal<br>Systems in Top-Down Design: From Pre-Silicon to<br>Post-Silicon          | Chatterjee, Abhijit      | Georgia Tech        |

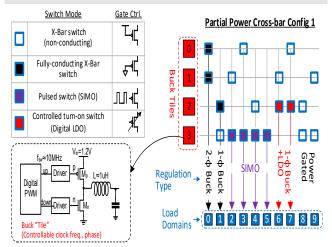

| 4  | 2712.006 | EE     | Robust, Efficient All-Digital SIMO Converters for<br>Future SOC Domains                                                                   | Sathe, Visvesh           | Univ. of Washington |

| 5  | 2712.007 | EE     | High-Resolution Low-Voltage Hybrid ADCs for Sensor<br>Interfaces                                                                          | Flynn, Michael           | Univ. of Michigan   |

| 6  | 2712.008 | EE     | Direct-Battery-to-Silicon Power Transfer in Advanced<br>Nanometer CMOS                                                                    | Harjani, Ramesh          | Univ. of Minnesota  |

| 7  | 2712.009 | EE     | Low Power Area Efficient Flexible-rate Energy<br>Proportional Serial Link Transceivers                                                    | Hanumolu, Pavan<br>Kumar | UIUC                |

| 8  | 2712.010 | FA     | Ringamp-assisted Circuits/Techniques and Next-<br>generation Ringamps                                                                     | Moon, Un-Ku              | Oregon State Univ.  |

| 9  | 2712.011 | FA     | Robust Reliable and Practical High Performance<br>References in Advanced Technologies                                                     | Geiger, Randall          | lowa St Univ.       |

| 10 | 2712.012 | EE     | EDAC and DCDC-Converter Co-Design for Addressing<br>Robustness Challenges in Emerging Architectures                                       | Seok, Mingoo             | Columbia            |

| 11 | 2712.013 | SS     | Reconfigurable MM-Wave Tx Architecture and<br>Antenna Interface with Active Impedance Synthesis<br>in Multi-Port Node-Conjugated Combiner | Sengupta, Kaushik        | Princeton           |

| 12 | 2712.014 | FA     | Leveraging CMOS Scaling in High Performance ADCS                                                                                          | Maghari, Nima            | Univ. of Florida    |

|    | Task     | Thrust | Title                                                                                                                                                          | Task Leader             | Institution                                  |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|

| 13 | 2712.015 | SS     | Area-Efficient On-Chip System-Level IEC ESD<br>Protection for High Speed Interface ICs                                                                         | Chen, Zhong             | U<br>Arkansas/Fayetteville                   |

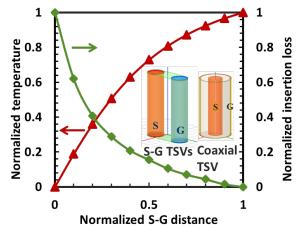

| 14 | 2712.016 | EE     | 3D IC Thermal Management Based on TSV<br>Placement Optimization and Novel Materials                                                                            | Lee, Jaeho              | UC/Irvine                                    |

| 15 | 2712.017 | SS     | Mitigating Reliability Issues in Analog Circuits                                                                                                               | Kim, Chris              | Univ. of Minnesota                           |

| 16 | 2712.018 | SS/EE  | Test Techniques to Approach Several Defect-per-<br>billion for Power ICs                                                                                       | Eisenstadt, William     | Univ. of Florida                             |

| 17 | 2712.019 | SS/EE  | Pre-computed Security Protocols for Energy<br>Harvested IoT                                                                                                    | Schaumont, Patrick      | Virginia Tech                                |

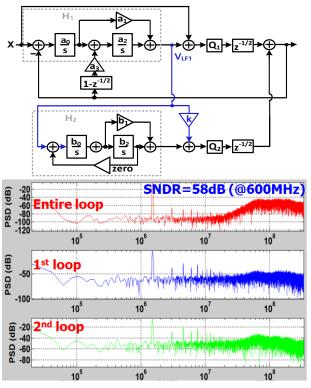

| 18 | 2712.020 | EE     | Low-Power Mostly Digital Time-Domain Delta-Sigma<br>ADCs for IoT                                                                                               | Sanyal, Arindam         | Univ. at Buffalo                             |

| 19 | 2712.021 | SS     | Distributed Silicon Circuits and Sensors in 3D-Printed<br>Systems for Wearable IoT Sensors                                                                     | Johnston, Matthew       | Oregon State Univ.                           |

| 20 | 2712.022 | SS     | Intrinsic Identifiers for Database-Free Remote<br>Authentication of IoT Edge Devices                                                                           | Bhunia, Swarup          | Univ. of Florida and<br>U. Illinois, Chicago |

| 21 | 2712.023 | EE     | Ultra-Low-Power Compressive Sensing Techniques<br>for IoT Applications                                                                                         | Sun, Nan                | UT/Austin                                    |

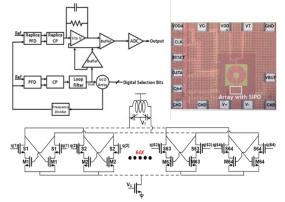

| 22 | 2712.024 | EE     | A System-In-Package Platform for Energy Harvesting<br>and Delivery for IoT Edge Devices                                                                        | Mukhopadhyay,<br>Saibal | Georgia Tech                                 |

| 23 | 2712.025 | FA     | Reduction of Low Frequency Noise Impact in Nano-<br>Scale CMOS Circuits                                                                                        | O, Kenneth              | UT/Dallas                                    |

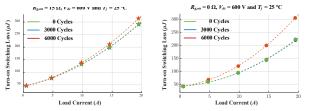

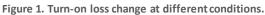

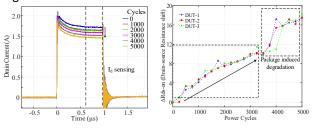

| 24 | 2712.026 | SS     | Fault Characterization and Degradation Monitoring of SiC Devices                                                                                               | Akin, Bilal             | UT/Dallas                                    |

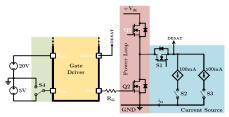

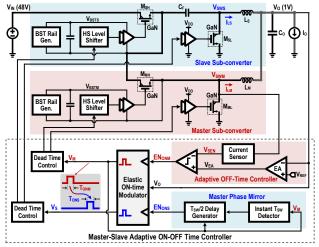

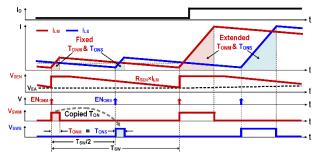

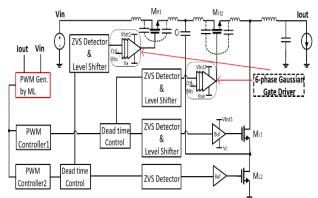

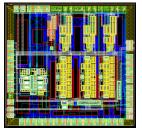

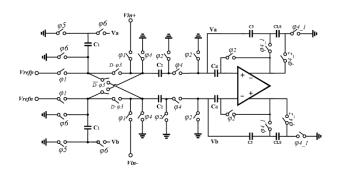

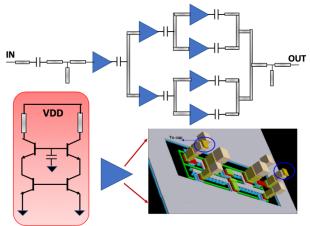

| 25 | 2712.027 | EE     | Gate Driving Techniques and Circuits for<br>Automotive-Use GaN Power Circuits                                                                                  | Ma, D. Brian            | UT/Dallas                                    |

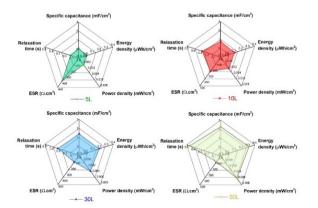

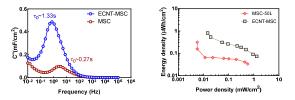

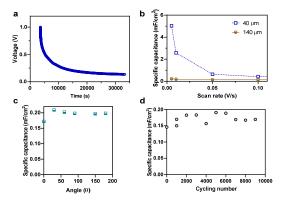

| 26 | 2712.028 | EE     | High Performance Micro-supercapacitor on a Chip<br>Based on a Hierarchical Network of Nitrogen Doped<br>Carbon Nanotube Sheets Supported MnO2<br>Nanoparticles | Lee, Gil                | UT/Dallas                                    |

|    | Task     | Thrust | Title                                                                                                                       | Task Leader             | Institution        |

|----|----------|--------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|

| 27 | 2712.029 | SS     | Novel Super-resolution and MIMO Techniques for<br>Automotive and Emerging Radar Applications                                | Torlak, Murat           | UT/Dallas          |

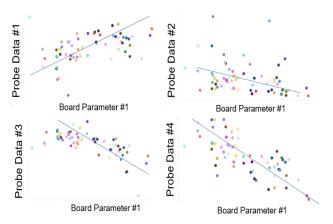

| 28 | 2712.031 | FA     | Adaptive Trimming and Testing of Analog/RF<br>Integrated Circuits (ICs)                                                     | Makris, Yiorgos         | UT/Dallas          |

| 29 | 2712.032 | FA     | Hierarchical Analog and Mixed-Signal Verification<br>Using Hybrid Formal and Machine Learning<br>Techniques                 | Li, Peng                | UC/Santa Barbara   |

| 30 | 2810.002 | SS/EE  | Security-Aware Dynamic Power Management for<br>System-on-Chips                                                              | Mukhopadhyay,<br>Saibal | Georgia Tech       |

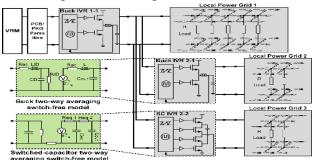

| 31 | 2810.003 | EE     | Integrated Voltage Regulator Management for<br>System-on-Chip Architectures                                                 | Zhang, Xuan             | Washington Univ.   |

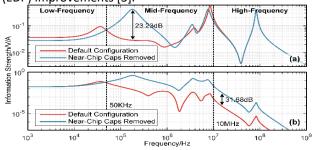

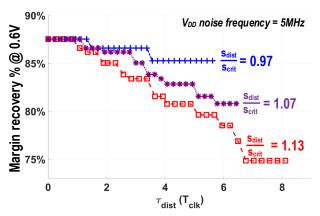

| 32 | 2810.005 | FA/SS  | Circuit Design for ESD and Supply Noise Mitigation                                                                          | Rosenbaum, Elyse        | UIUC               |

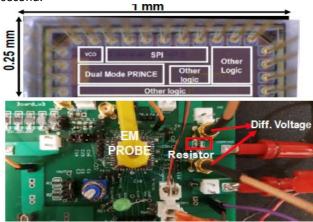

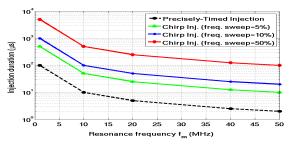

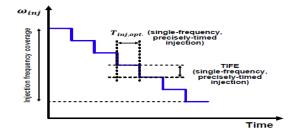

| 33 | 2810.006 | EE     | Combating Unprecedented Efficiency, Noise and<br>Frequency Challenges in Modern High Current<br>Integrated Power Converters | Ma, D. Brian            | UT/Dallas          |

| 34 | 2810.007 | FA     | Fully Integrated Phase Noise Cancellation<br>Techniques                                                                     | Niknejad, Ali           | UC/Berkeley        |

| 35 | 2810.008 | EE     | Circuit Techniques for Fast Start-Up of Crystal<br>Oscillators                                                              | Pamarti, Sudhakar       | UCLA               |

| 36 | 2810.009 | EE/FA  | Mixed-Signal Building Blocks for Ultra-low Power<br>Wireless Sensor Nodes                                                   | Sylvester, Dennis       | Univ. of Michigan  |

| 37 | 2810.010 | EE     | GS/s ADC Based Cycle-to-Cycle Closed-Loop Adaptive<br>Smart Driver for High-Performance SiC/GaN Power<br>Devices            | Gui, Ping               | SMU                |

| 38 | 2810.011 | EE     | Micro-Power Analog-to-Digital Data Converters for<br>Sensor Interfaces                                                      | Temes, Gabor            | Oregon State Univ. |

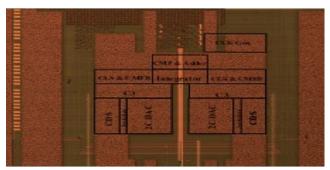

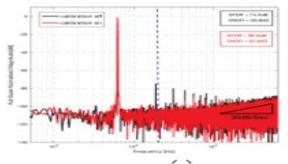

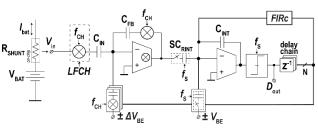

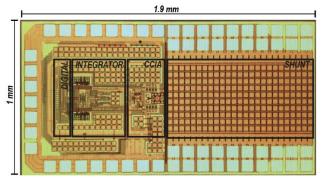

| 39 | 2810.012 | EE     | NPSense - Nano-Power Current Sensing                                                                                        | Makinwa, Kofi           | Delft University   |

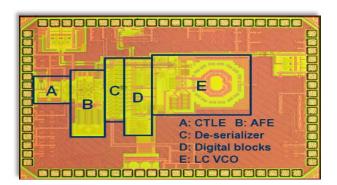

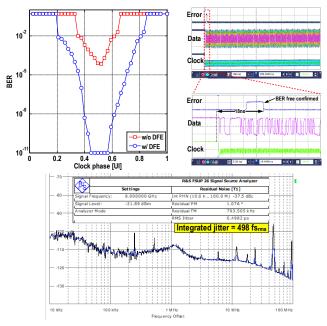

| 40 | 2810.013 | FA     | Frequency-Domain ADC-Based Serial Link Receiver<br>Architectures for 100+Gb/s Serial Links                                  | Palermo, Samuel         | TEES               |

|    | Task     | Thrust | Title                                                                                                                                                          | Task Leader             | Institution                                      |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|

| 41 | 2810.014 | SS     | Deep Learning Solutions for ADAS: From Algorithms<br>to Real-World Driving Evaluations                                                                         | Busso, Carlos           | UT/Dallas                                        |

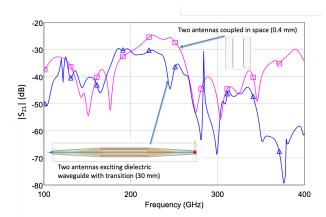

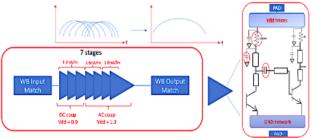

| 42 | 2810.015 | FA     | Demonstration of 120-Gbps Dielectric Waveguide<br>Communication Using Frequency Division<br>Multiplexing (FDM) and Polarization Division<br>Multiplexing (PDM) | O, Kenneth              | UT/Dallas                                        |

| 43 | 2810.016 | SS     | Condition Monitoring of Industrial/Automotive Drive<br>Components through Leakage Flux                                                                         | Akin, Bilal             | UT/Dallas                                        |

| 44 | 2810.017 | SS     | Reliability Study of E-mode GaN HEMT Devices                                                                                                                   | Kim, Moon               | UT/Dallas                                        |

| 45 | 2810.018 | FA     | Transition Design for High Data Rate Links at<br>Submillimeter Wave Frequencies                                                                                | Henderson,<br>Rashaunda | UT/Dallas                                        |

| 46 | 2810.019 | FA     | Design Automation for Coverage Management in<br>Analog and Mixed-Signal SOCs                                                                                   | Dasgupta, Pallab        | Indian Institute of<br>Tech. Kharagpur<br>(IITK) |

| 47 | 2810.020 | FA     | Analog/Mixed-Signal RF Circuit Time Domain<br>Sensitivity and Its Applications                                                                                 | Rohrer, Ronald          | SMU                                              |

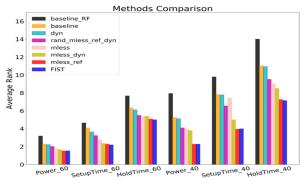

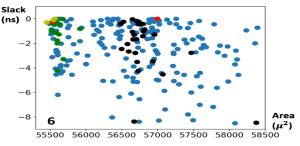

| 48 | 2810.021 | SS     | A Collaborative Machine Learning Approach to Fast<br>and High-Fidelity Design Prediction                                                                       | Hu, Jiang               | TEES and Duke<br>University                      |

| 49 | 2810.022 | SS     | A Collaborative Machine Learning Approach to Fast<br>and High-Fidelity Design Prediction                                                                       | Chen, Yiran             | Duke Univeristy and<br>TEES                      |

| 50 | 2810.023 | SS     | Machine Learning Driven Automatic Mixed-Signal<br>Design Verification-Validation for Automotive<br>Applications                                                | Chatterjee, Abhijit     | Georgia Tech                                     |

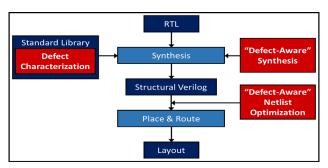

| 51 | 2810.025 | SS     | Machine Learning-Based Layout Analysis and Netlist<br>Optimization for Defect Tolerance and Design<br>Robustness to Process Imperfections and Variations       | Makris, Yiorgos         | UT/Dallas                                        |

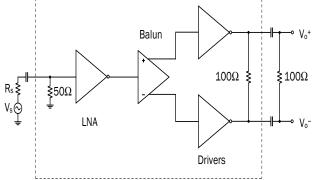

| 52 | 2810.026 | FA     | Low Noise Balun Pre-Power Amplifier                                                                                                                            | Nauta, Bram             | University of Twente                             |

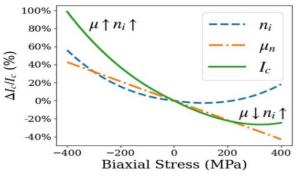

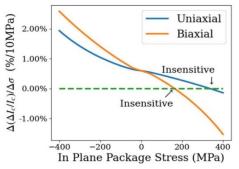

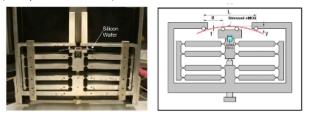

| 53 | 2810.027 | SS     | Measurement and Modeling of Stress/Strain on<br>Analog Transistor and Circuit<br>Parameters                                                                    | Thompson, Scott         | University of Florida                            |

| 54 | 2810.028 | FA     | Robust ATE Multi-Site HW Design to Enable Effective<br>Analog Performance Testing in Analog-Mixed-Signal<br>(AMS) SoCs                                         | Chen, Degang            | lowa State U.                                    |

|    | Task     | Thrust | Title                                                                                                                                  | Task Leader        | Institution      |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|

| 55 | 2810.029 | FA     | 170GHz – 260GHz Wideband PA and LNA Design in<br>Silicon                                                                               | Babakhani, Aydin   | UCLA             |

| 56 | 2810.030 | FA     | Neural Network Recognition & On-Chip Online<br>Learning with STT-MRAM                                                                  | Friedman, Joseph   | UT/ Dallas       |

| 57 | 2810.031 | FA     | Development and Asssessment of Machine Learning<br>Based Analog and Mixed-Signal Verification                                          | Li, Peng           | UC/Santa Barbara |

| 58 | 2810.032 | EE     | DRIVR: A Digital, Re-configurable, Unified Clock-<br>Power (UniCaP) Fabric for Energy-Efficient SoCs                                   | Sathe, Visvesh     | U. of Washington |

| 59 | 2810.033 | FA     | Interleaved Noise-Shaping SAR ADCs for High-Speed<br>and High-Resolution                                                               | Flynn, Michael     | U. of Michigan   |

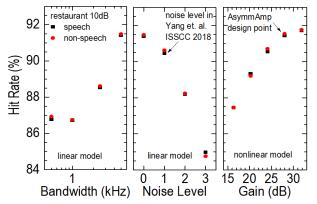

| 60 | 2810.034 | EE     | Always-on Keyword Spotting based on Analog-<br>Mixed-Signal Computing Hardware                                                         | Seok, Mingoo       | Columbia         |

| 61 | 2810.035 | EE     | Computationally Controlled Integrated Voltage<br>Regulators                                                                            | Sathe, Visvesh     | U. of Washington |

| 62 | 2810.036 | FA     | Highly Stable Integrated Frequency References                                                                                          | Hanumolu, Pavan    | UIUC             |

| 63 | 2810.037 | FA     | High-performance Ringamp-based ADCs                                                                                                    | Moon, Un-Ku        | Oregon State U.  |

| 64 | 2810.038 | SS     | Extreme Temperature Digital, Analog, and Mixed-<br>Signal Circuits (ET-DAMS)                                                           | Kim, Chris         | U. of Minnesota  |

| 65 | 2810.039 | EE     | Development of Compact and Low Cost Fully<br>Integrated DC-DC Converter with Resonant Gate<br>Drive and Intelligent Transient Response | Gu, Jie            | Northwestern U.  |

| 66 | 2810.040 | EE     | Hybrid/Resonant Sc Converters With Integrated Lc<br>Resonator For High-Density Monolithic Power<br>Delivery                            | Stauth, Jason      | Dartmouth        |

| 67 | 2810.041 | SS     | ESD Protection for IO Operating at 56 Gb/s and<br>Beyond                                                                               | Rosenbaum, Elyse   | UIUC             |

| 68 | 2810.042 | EE     | Digitally Enhanced High Efficiency, Fast Settling<br>Augmented DCDC Converters                                                         | Bakkaloglu, Bertan | Arizona State    |

|    | Task     | Thrust | Title                                                                                                                                                      | Task Leader             | Institution      |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|

| 69 | 2810.043 | FA     | Analog Optimization Hybridizing Designer's Intent<br>and Machine Learning                                                                                  | Li, Peng                | UC/Santa Barbara |

| 70 | 2810.044 | FA     | Hierarchical Characterization and Calibration of RF/Analog Circuits Using Lightweight Built-in Sensors                                                     | Ozev, Sule              | Arizona State    |

| 71 | 2810.046 | SS     | Generating Current Constraints for Electromigration<br>Safety                                                                                              | Najm, Farid             | U. of Toronto    |

| 72 | 2810.047 | SS     | Architecture and DfT methods for improving life<br>time reliability and functional safety of electronic<br>circuits and systems out of application context | Chen, Degang            | lowa State U.    |

| 73 | 2810.048 | SS     | Characterization and Mitigation of Electromigration<br>Effects in Advanced Technology Nodes                                                                | Kim, Chris              | U. of Minnesota  |

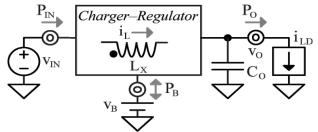

| 74 | 2810.049 | EE     | 1-W Battery-Charging CMOS Buck Regulator                                                                                                                   | Rincon-Mora,<br>Gabriel | Georgia Tech     |

# Table 2: Funded research projects at TxACE by SRC task identification number (FA: Fundamental Analog, EE: Energy Efficiency, SS: Safety, Security and Health Care)

### ACCOMPLISHMENTS

In the past year, TxACE has made significant research progress. Table 3 summarizes the number of publications and inventions resulting from the TxACE research during May 2019 to April 2020, while Table 4 lists the major research accomplishments for the Center during the period. The TxACE researchers have published 48 conference papers and 29 journal papers. They have also made 2 invention disclosure, filed 5 patent applications, and were granted 2 patents. The list of publications is included as Appendix I. Following the tabulation, brief summaries of each project are provided.

#### Table 3. TxACE number of publications (May 2019 through April 2020)

| Conference<br>Papers | Jourr | nal Papers | Invention<br>Disclosures | Patents Filed | Patents Granted |

|----------------------|-------|------------|--------------------------|---------------|-----------------|

| 48                   |       | 29         | 2                        | 5             | 2               |

| Category                            | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

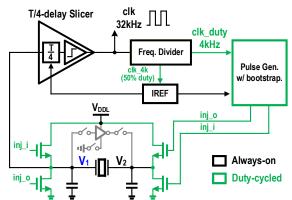

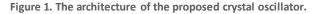

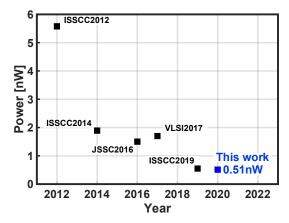

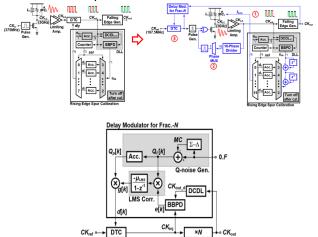

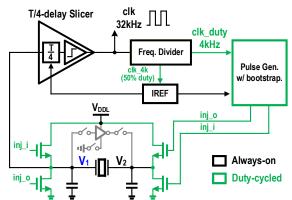

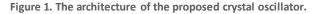

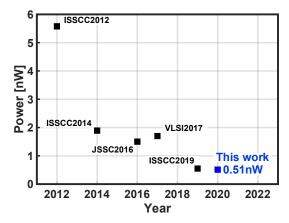

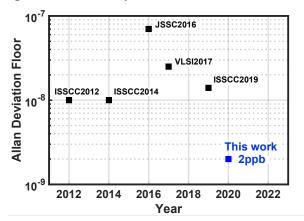

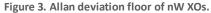

| Fundamental<br>Analog<br>(Circuits) | Ultra-low power crystal oscillators (XOs) are key components in wearable, IoT, and mobile applications. Using a frequency-divided high-energy-to-noise-ratio pulse injection allows the crystal to run freely for a longer time between injections, thus improving long-term frequency stability and reducing injection overheard. Fabricated in 40-nm CMOS, a prototype 32kHz XO consumes only 0.51nW and achieves 2ppb Allan deviation, which is 5x lower compared to that achieved by state-of-the-art nW-XOs. (2810.009, PI: D. Sylvester & D. Blaauw, U Michigan) |

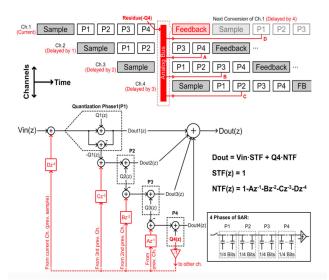

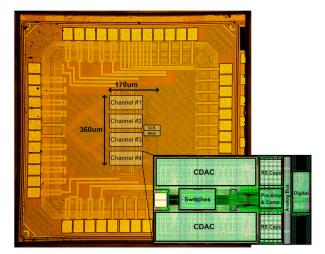

| Fundamental<br>Analog<br>(Circuits) | Higher-order noise shaping in successive approximation register analog to digital converter (SAR ADC) is demonstrated using a cascaded-noise-shaping (CaNS) SAR architecture. By cascading two 2nd-order NS stages, a 4th-order noise-transfer function is realized while consuming similar power and area to a 2nd-order NS-SAR. Fabricated in 28-nm CMOS, the prototype CaNS-ADC occupying 0.02mm <sup>2</sup> achieves 88dB SNDR over a 100kHz bandwidth while consuming only 120µW. (2810.033, PI: M. Flynn, U Michigan)                                           |

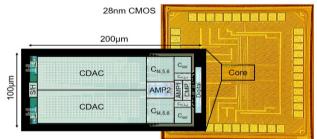

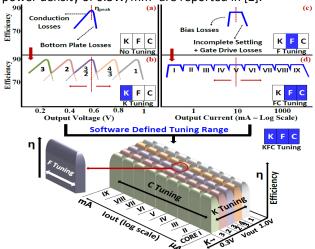

| Energy Efficiency<br>(Circuits)     | Power IC's from a battery involves several power conversion stages, usually requiring a high voltage buck converter and LDOs. A direct battery-to-silicon prototype demonstrates that DC-DC conversion can be accomplished in CMOS using a multi-resonant coupled-inductor with 80% efficiency over a wide conversion rage ( $0.2 - 0.8$ ). The output voltage is then regulated using a digital LDO with zero steady-state output voltage ripple. (2712.008, PI: R. Harjani, U Minnesota)                                                                             |

| Energy Efficiency<br>(Circuits)     | Ultra low-power compressive sensing techniques for IoT applications have the potential to greatly improve the energy efficiency of edge devices. A compressive sensing coding scheme for a CMOS imager uses a mixed-signal switched capacitor matrix multiplier. This is the first CMOS image sensor that achieves single-shot compressive sensing using Nyquist-rate ADCs, improving the state-of-art energy efficiency by >20x. (2717.023, PI: N. Sun, UT Austin)                                                                                                    |

#### Table 4. Major TxACE Research Accomplishments (May 2019 through April 2020)

| Energy Efficiency<br>(Circuits)                  | A hybrid resonant switched capacitor converter with an integrated LC resonator<br>is demonstrated for high-density power delivery. A designed and tested merged<br>LC resonator with on-chip spiral magnetics results in a factor of two<br>improvement in power density with higher efficiency relative to comparable<br>pure switched-capacitor implementations. (2810.040, PI: J. Stauth, Dartmouth)                                                                    |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

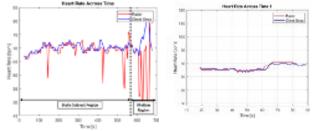

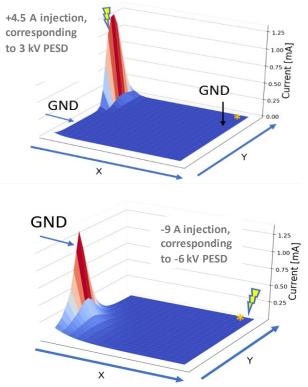

| Safety, Security and<br>Health Care<br>(Systems) | This project is developing a co-design methodology for ESD-protected front-end circuits in 56-Gbps receivers that employ PAM4 signaling. Defining a capacitance budget as a function only of the data-rate and the technology node is overly simplistic and may lead one to unnecessarily limit a component ESD reliability. Selecting ESD protection devices based on an eye diagram analysis reduces circuit performance degradation. (2810.041, PI: E. Rosenbaum, UIUC) |

| Safety, Security and<br>Health Care<br>(Systems) | This project investigates vital sign detection algorithms using mm-Wave frequency modulated continuous wave (FMCW) radar. To date, results have shown effective tracking of a heart rate across time, with mean squared heart rate errors of approximately 1 bpm for a static single subject when compared to a wearable chest strap. (2712.029, PI: M. Torlak, UT Dallas)                                                                                                 |

# Safety, Security and Health Care Thrust

| Category                                            | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

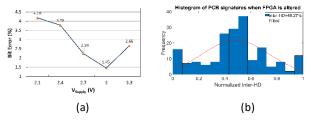

| Safety,<br>Security and<br>Health Care<br>(Systems) | This project is developing a co-design methodology for ESD-protected front-<br>end circuits in-54 Gbps receivers. Initial work focused on a study of "ESD<br>capacitance budgets," demonstrating that an eye diagram analysis is needed to<br>determine when the ESD protection will unacceptably compromise the circuit<br>performance. Case studies made apparent that defining a capacitance budget<br>as a function only of the data-rate and the technology node may lead one to<br>unnecessarily limit a component ESD reliability or, conversely, force the<br>designer to unnecessarily increase the chip power or accept a reduced error<br>rate. (2810.041, E. Rosenbaum, UIUC) |  |

| Safety,<br>Security and<br>Health Care<br>(Systems) | As opposed to camera-based sensors, millimeter wave (mm-Wave) radar technology provides the ability to meet privacy requirements in addition to being unobtrusive and non-intrusive. This project investigates vital sign detection algorithms using mm-Wave frequency modulated continuous wave (FMCW) radars. To date, results have shown effective tracking of a heart rate across time, with mean squared heart rate errors of approximately 1 bpm for a static single subject when compared to a wearable chest strap. (2712.029, M. Torlak, UT Dallas)                                                                                                                              |  |

| Safety,<br>Security and<br>Health Care<br>(Systems) | There is an emerging set of applications requiring stretchable, compliant electronics, including wearable devices, instrumented fabrics, and soft robots with distribute sensors and computation. Over the course of this project, progress has been made in printing multi-layer stretchable circuits using discrete components, in extended strain testing of liquid metal paste material, and in development of compact modeling frameworks for stretchable interconnects. (2712.021, M. Johnston & Y. Mengüc, Oregon State University)                                                                                                                                                |  |

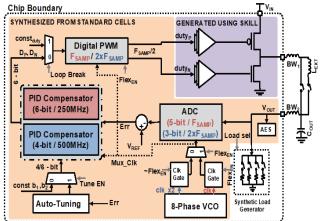

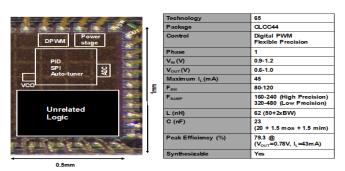

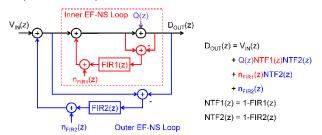

### TASK 2712.002, ON-LINE SELF-TESTING AND SELF-TUNING OF INTEGRATED VOLTAGE REGULATORS SAIBAL MUKHOPADHYAY, GEORGIA INSTITUTE OF TECHNOLOGY, SAIBAL@ECE.GATECH.EDU

#### SIGNIFICANCE AND OBJECTIVES

The proposed research will develop low-complexity algorithms and low-overhead all-digital self-testing and self-tuning architecture for high-frequency IVRs. The proposal will focus on a digitally controlled fully integrated inductive VR (FIVR), digital low-dropout regulators (DLDO), and power delivery system with a FIVR and multiple distributed DLDOs.

#### TECHNICAL APPROACH

The challenge for testing/tuning of IVRs is the presence of high frequency closed-loop control. The proposed approach is based on the principle that in a system with an IVR and digital core(s), the testing/tuning should focus on system performance rather than the IVR in isolation. We propose to characterize the output voltage variation that ultimately determines the performance of the digital load. We consider large signal perturbations (load and reference steps) to excite the transient noise in the IVR's output, and tune the IVR's loop to minimize the noise. Finally, we explore co-tuning of IVR and processor.

#### SUMMARY OF RESULTS

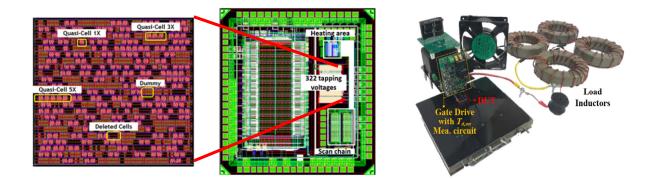

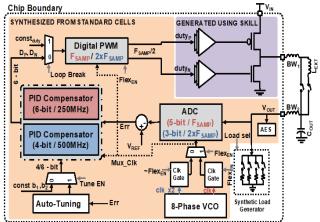

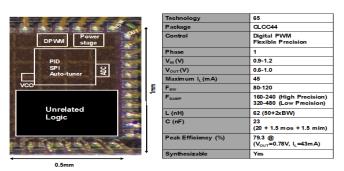

A fully synthesized integrated inductive buck regulator with flexible precision variable frequency feedback loop implemented in 65-nm CMOS process using an automated design and GDSII generation flow is demonstrated. The design demonstrates  $0.52V/\mu s$  output ramp and 200ns response time to 30mA/75ps load transient in a high precision mode with 120MHz switching frequency. The peak efficiency is 79.3% at 0.78V output and 43mA load current.

Figure 1. The architecture of full-synthesized architecture with on-line tuning.

Figure 2. The summary of the test-chip.

The degradation of the transient performance and power conversion efficiency of on-chip VRs due to NBTI have been investigated. The measurement show that NBTI induced shifts in the power stage resistance have much smaller effect on the IVR compared to DLDOs.

Figure 3. The measurement results showing impact of of aging on inductive VR and digital LDO.

Keywords: Integrated voltage regulator, self-testing,

#### INDUSTRY INTERACTIONS

Intel, NXP

#### MAJOR PAPERS/PATENTS

[1] A. Singh, et al., "A Digital Low-Dropout Regulator with Auto-Tuned PID Compensator and Dynamic Gain Control for Improved Transient Performance under Process Variations and Aging," IEEE TPEL, March 2020.

[2] V. Chekuri, et al., "Auto-tuning of Integrated Inductive Voltage Regulator using On-chip Delay Sensor to Tolerate Process and Passive Variations," IEEE TVLSI, Aug. 2019.

[3] V. Chekuri, et al., "A Fully Synthesized Integrated Buck Regulator with Auto-generated GDS-II in 65nm CMOS Process," IEEE CICC, March 2020.

[4] (Invited) V. Chekuri, et al., "Aging Challenges in On-chip Voltage Regulator Design," International Reliability Physics Symposium (IRPS), April 2020.

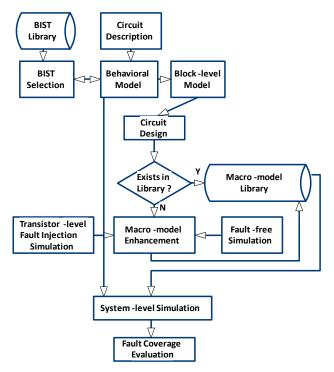

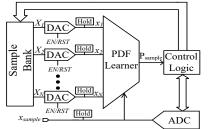

This project aims at (a) designing a library of BIST blocks that can be re-designed with minimal effort, (b) developing measurement techniques that do not rely on detailed knowledge of internal BIST parameters, and (c) developing a BIST advisor toolflow for system-level BIST insertion and evaluation.

#### **TECHNICAL APPROACH**

We have divided this problem into two parallel threads. First, we have developed a library of BIST components, including a gain measurement unit, a phase mismatch measurement unit, a PRBS injection unit, a cross correlator, and a programmable OPAMP-less ADC. Second, the BIST advisor toolflow takes into account multiple BIST options and evaluates them in terms of fault coverage and hardware cost to provide viable options for the designers.

#### SUMMARY OF RESULTS

During this project, we have developed a BIST insertion flow. Our BIST approach consists of two parts, first one is a target specific part where we develop a methodology to apply and observe PRBS in order to obtain a loop transfer

function, second part is evaluation of different testing approaches in terms of fault coverage. The latter also considers the simulation shortcomings and includes the application of macro-modelling to shorten the simulation time which may be prohibitively high when a high number of potential faults could be inserted into circuits and also considering challenges of simulating circuits which take a very long time to simulate.

The flow of our testing approach, which is called BIST advisor is summarized in Figure 1. BIST library in the flow chart consists of blocks designed such as PRBS generation, digital cross correlator etc. For any target application there may be some different blocks needed. For example, PLL and LDO use the same 12-Bit PRBS generation and same digital cross correlator consisting of up/down counter, however since LDO output is analog it requires a 1-bit analog-to-digital converter. The first step in the process is to develop a methodology to apply and cross correlate PRBS signals, which is explained in depth in the previous sections. Next task is to decide whether circuit simulation could be done for fault evaluation considering the simulation time for the set of fault cases. We want to macro model faulty behavior of a circuit so that it can be simulated quickly. In order to do that first, non-faulty behavior should be modelled. Matlab or any other behavioral modelling tool can be used for this purpose. Block level simulations are very fast, thus it enables fast modelling. After non-faulty block in a loop is modelled, its features which effects the loop behavior is extracted. Then faults are inserted and model is extracted based upon these features.

#### Keywords: Analog BIST, Fault Simulation

#### INDUSTRY INTERACTIONS

Texas Instruments, NXP

#### MAJOR PAPERS/PATENTS

[1] Ince, Mehmet, and Sule Ozev. "Digital Defect Based Built-in Self-Test for Low Dropout Voltage Regulators." In IEEE European Test Symposium (ETS), pp. 1-2. IEEE, 2020.

Figure 1. BIST insertion flow.

### TASK 2712.013, RECONFIGURABLE MM-WAVE TX ARCHITECTURE AND ANTENNA INTERFACE WITH ACTIVE IMPEDANCE SYNTHESIS IN MULTI-PORT NODE-CONJUGATED COMBINER KAUSHIK SENGUPTA, PRINCETON UNIVERSITY, KAUSHIKS@PRINCETON.EDU

#### SIGNIFICANCE AND OBJECTIVES

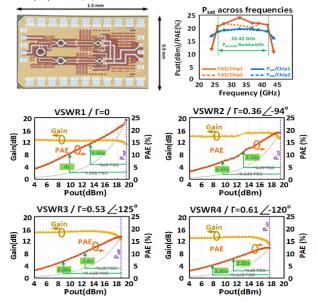

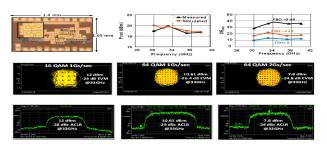

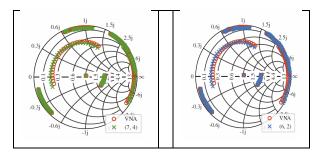

We demonstrated a generalized broadband VSWRreconfigurable PA architecture with a multi-port DAC based topology across 26-40 GHz. We also reported the first mm-Wave Load Modulated Balanced Amplifier (LMBA) that aims broadband and back-off efficiency in the 5G bands. The paper has been **is a Best student paper finalist at IMS 2020.**

#### **TECHNICAL APPROACH**

We proposed a generalized method of loadpulling to overcome VSWR in a reconfigurable fashion between 26-40 GHz. For the LMBA, we presented the first mmWave load modulated balanced PA architecture with adaptive biasing for enhanced linearity.

#### SUMMARY OF RESULTS

The VSWR-tolerant RF-in and RF-out PA is based on the proposed asymmetrical architecture to allow for broadband operation over the multiple bands at 28GHz, 37GHz, and 39GHz while allowing tolerance towards VSWR events up to 4:1. The initial results were published in [1], and we presented an entire analytical framework and theoretical limits and design techniques in the special issue paper in [2].

Figure 1. Schematic of the broadband VSWR-tolerant PA architecture in 65-nm CMOS operating across 26-40 GHz.

Figure 2. Continuous wave measurements of LMBA across 30-40 GHz along with drive ups at 33,36 and 40 GHz. EVM and ACLR vs average output power for a 16/64 QAM signal at 33 GHz. 16QAM and 64QAM constellations and spectrum.

The load modulated balanced amplifier chip micrograph is shown in Fig. 2. The architecture is implemented with a transformer-based hybrid at input and output to allow wideband power combining and achieve high isolation with a control PA for load-modulation and back-off efficiency enhancement across 30-40 GHz. For enhanced linearity, an integrated adaptive biasing is integrated onchip allowing superior ACLR performance across 30-40 GHz. The PA achieves 18.5-20 dBm, output drain efficiency >30% across 30-40 GHz, and demonstrates EVM of -26.4 dB and ACLR of -29 dBc at an average output power of 10.6 dBm for 64-QAM at 1GS/s. To the best of the authors' knowledge, this is the first load-modulated balanced PA at mmWave in silicon.

Keywords: mmWave, PA, broadband, load modulation, 5G

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, NXP

#### MAJOR PAPERS/PATENTS

[1] C.R.Chappidi and K.Sengupta, "A 26-42 GHz Broadband, Back-off efficient and VSWR Tolerant CMOS Power Amplifier Architecture for 5G Applications," VLSI 2019.

[2] C.R.Chappidi, T.Sharma, Z.Lu and K.Sengupta, "Multiport-Active Load-pulling for mm-Wave 5G Power Amplifiers: Bandwidth, Back-off Efficiency and VSWR Tolerance," *IEEE TMTT* special Issue on mmw-PAs.

[3] C.R.Chappidi, T.Sharma, Z.Lu and K.Sengupta, "Load Modulated Balanced mm-Wave CMOS PA with Integrated Linearity Enhancement for 5G applications" *IMS 2020*.

[4] Kaushik Sengupta and Chandrakanth Chappidi, Load modulated balanced mm-Wave PA architecture, provisional patent filed.

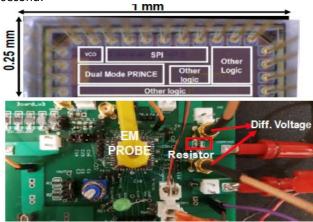

### TASK 2712.015, AREA-EFFICIENT ON-CHIP SYSTEM-LEVEL IEC ESD PROTECTION FOR HIGH SPEED INTERFACE IC'S ZHONG CHEN, UNIVERSITY OF ARKANSAS, FAYETTEVILLE, CHENZ@UARK.EDU

#### SIGNIFICANCE AND OBJECTIVES

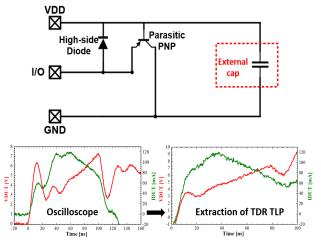

Area-efficient, low-capacitance, on-chip system-level IEC ESD protection solutions for high-speed interface ICs will be designed, fabricated and characterized. Device physics for substrate parasitic PNP structure in  $P^+/N$ -well diodes will be modeled.

#### **TECHNICAL APPROACH**

To reduce the total ESD device areas and reduce the parasitic capacitance, our approach is to utilize the inherent parasitic PNP structure in the high-side ESD diode as a parallel path to shunt the ESD discharge current. The key for this approach is to understand and adjust the characteristics of substrate PNP structures, such that the triggering and ESD clamping voltage of parasitic PNP structure is within the specific ESD protection window. Meanwhile, the clamping voltage of the primary ESD protection path needs to be higher than the triggering voltage of the parasitic PNP device.

#### SUMMARY OF RESULTS

First, ESD diodes with various layout designs were fabricated in the UMC 65-nm CMOS process. The objective is to evaluate which type of diodes can achieve better ESD performance (e.g., thermal failure current  $I_{t2}$ ) within the same layout area for given  $I_{t2}$ /Area. Moreover, capacitance of these devices is investigated. Different metal routings were designed for different diode structures to compare the capacitance. The TLP I-V measurements show that the island-type diodes achieve higher  $I_{t2}$ /Area than the finger-type diodes, but also have higher capacitance. Thus, the figure-of-merit,  $I_{t2}/C$  is introduced to supplement the performance evaluation of the device.

Second, ESD characterization of dual-diode ESD protection with a primary ESD cell (2.5V PMOS and 2.5V NMOS were designed) was conducted. We expected that the parasitic substrate PNP should not be triggered before the turn-on of the primary ESD cell. However, the measurements indicate that parasitic substrate PNP triggers before the primary ESD due to higher triggering voltage of the primary ESD cell. The triggering voltage on this parasitic substrate PNP has been re-designed in a new tapeout.

Third, in the real applications of the dual-diode ESD protection, parasitic capacitance existing in the power

Figure 1. Current injection testing configuration with an external capacitor is used to analyze the effect of injected current on the parasitic PNP triggering behavior. Time domain extraction methodology is used to get the I-V curve across the capacitor.

supply or board might have some effects on ESD behaviors of the parasitic substrate PNP. The parasitic capacitance will introduce transient displacement current that will be injected into the forward-biased ESD diode. This transient current may affect the triggering of the parasitic substrate PNP. The testing configuration shown in Figure 1 is used to evaluate this effect. Through the direct comparison of the TLP I-V curves with and without the external capacitor, we can observe that the triggering point decreases with the external capacitor. A time domain extraction of a single TLP waveform has been performed to characterize the injected current level generated by the external capacitor. The actual I-V curve across the external capacitor can be extracted from the waveforms captured by the oscilloscope (Figure 1). More TLP measurements are going to be performed to evaluate the effects of current injection on the parasitic PNP triggering.

Keywords: ESD, PNP, IEC, TCAD, Current injection

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] Zhong Chen, Muhammad Ali, Hui Wang, "ESD Selfprotection of Output Circuitry Using Substrate Bipolar Structure," Provisional patent filed.

[2] W. Hui, et al, "Area-efficient Dual-diode ESD Protection Based on Parasitic Bipolar Device for High-speed Interface ICs," Under revision for Journal of Electrostatics.

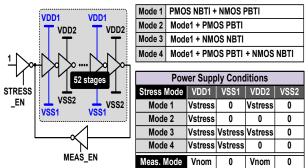

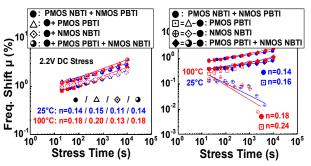

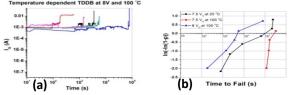

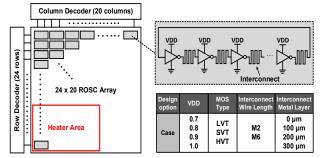

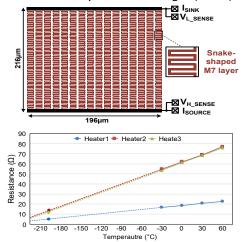

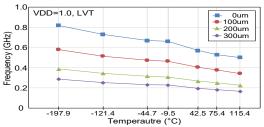

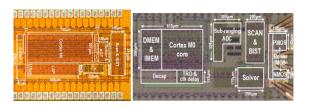

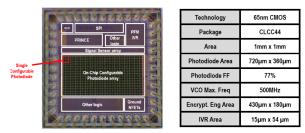

An on-chip reliability monitor capable of characterizing all four types of bias temperature instability (BTI) modes is proposed. Stressed ring oscillators with independent dual power rails are implemented for this purpose. Extensive BTI data was collected from a 65-nm ROSC array under different stress conditions.

#### **TECHNICAL APPROACH**

In this work, we demonstrate for the first time, an onchip beat frequency based monitor circuit capable of characterizing frequency shifts caused by all four BTI modes. The main innovation is a ring oscillator (ROSC) circuit with dual power rails enabling different BTI stress modes. The beat frequency detection scheme offers a high frequency measurement precision (>0.01%) with minimal unwanted device recovery during measurements owing to the short stress interrupt time (>1µs).

#### SUMMARY OF RESULTS

The proposed ring oscillator circuit for separately measuring all four BTI induced shifts shown in Fig. 1 consists of two power rails, a 52-stage inverter chain, and two tri-state inverters. During stress mode, the ROSC is configured as an open loop inverter chain whose input is set to 0V. To apply different BTI stress modes to the inverter chain, two sets of power supplies are used; VDD1 and VSS1 for odd inverter stages and VDD2 and VSS2 for even inverter stages. In measurement mode, the inverter chain is configured into a ROSC and the power rail voltages are switched to the nominal VDD and VSS voltages.

Figure 1. (left) Proposed dual power rail ROSC. (upper right) BTI stress modes. (lower right) Power supply configuration.

The test chip shown in Fig. 2 consists of a 48 ROSC array grouped into four 12 ROSC sub-arrays, 3 reference ROSCs, and 3 parallel beat frequency detection circuits. Each subarray is assigned to one of the four different stress modes, and power switches control the two VDD and VSS pairs depending on the stress mode. Before applying stress, we measured the frequency distribution of fresh ROSCs. The frequencies of the three reference ROSCs were separated using on-chip trimming capacitors to cover the frequency range (~3%) of the ROSC array. During stress mode, one ROSC is selected at a time for frequency measurements using column and row decoders while the other ROSCs are kept in stress mode. The multiplexed output of the selected DUT is compared with the three reference ROSC frequencies using the beat frequency detection circuits.

| Decoder &        | Process          | 65nm GP                                       |

|------------------|------------------|-----------------------------------------------|

| Control Logic    | BTI Stress Modes | PMOS NBTI, NMOS PBTI,<br>PMOS PBTI, NMOS NBTI |

| DUT ROSC         | Core/IO Supply   | 1.0V / 2.5V                                   |

| Array 👸          | Stress Voltage   | 1.8V, 2.2V, 2.6V                              |

| (48 cells) 이 것 문 | Meas. Voltage    | 0.9V                                          |

| 100um            | DUT Device       | Core Deivce                                   |

| 2 H I            | Area             | 425 x 360 µm <sup>2</sup>                     |

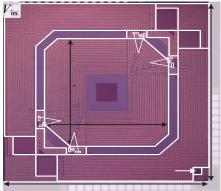

Figure 2. Die photo and chip specification summary.

Frequency shifts measured from the 65nm test chip are shown in Fig. 3. All 4 BTI components have a positive correlation with temperature while the power law exponent increases modestly with increasing temperatures. To extract the individual BTI components, we took the difference between the frequency shifts measured under different stress modes. Measured results show that PMOS NBTI is dominant followed by PMOS PBTI and NMOS NBTI.

Figure 3. Test chip data showing combined (left) and individual (right) BTI induced shifts.

**Keywords:** bias temperature instability, analog reliability, ring oscillators, beat frequency, stress experiments

#### INDUSTRY INTERACTIONS

Texas Instruments, NXP

#### MAJOR PAPERS/PATENTS

[1] G. Park et al., "An All BTI (PMOS NBTI, PMOS PBTI, NMOS NBTI, NMOS PBTI) Odometer based on a Dual Power Rail Ring Oscillator Array," (in preparation)

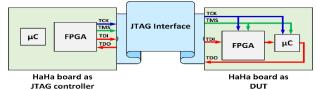

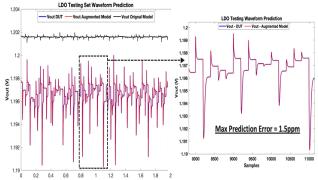

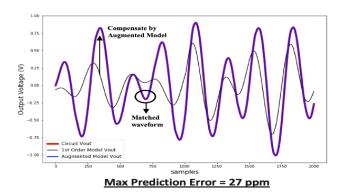

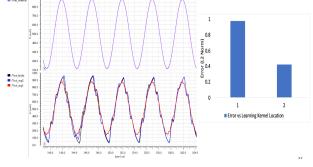

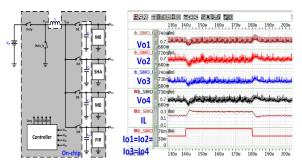

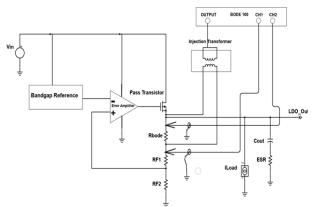

This research designed, simulated and tested custom LDO and Buck Converter power ICs using additional baredie test points to better anticipate part failures. The goal was to improve yield by culling power ICs with outlier subcircuit performance. Additional work characterized small-signal LDO control loop gain using IC external pins.

#### **TECHNICAL APPROACH**

Task researchers developed novel 65-mn CMOS LDOs and Buck Converter designs with internal IC test points for enhancing testing. Analyses and simulations of these designs were used to determine subcircuit performance inside the LDO and Buck Converter. Based on this work, a 65-nm CMOS LDO test IC and a Buck converter test IC were designed, fabricated and tested. The functional LDO Test IC was used to demostrate on-chip control loop gain and phase response measurements. Researchers also investigated methods to do control loop characterization quickly on ATE.

#### SUMMARY OF RESULTS

This year the project researchers 1) packaged a 65-nm CMOS Buck converter IC, made a custom test board for the converter and performed converter measurements, 2) developed a technique in collaboration with TI engineers to characterize LDO control-loop circuit elements from LDO measurements, and 3) developed test boards and performed small-signal control-loop measurements of an LDO test IC.

Also, researchers used measurements to identify outlier capacitors in the LDO control-loop from LDO IC pin measurements. This work was performed at TI Tucson, AZ.

The Buck converter IC testing strategy used extra probe points for DC and analog test on die. The researchers were guided by the SRC/TI program liaison engineers to develop a Buck converter test IC with an advanced Average Current Mode (ACM)-based control loop design. The researchers received 65-nm CMOS Buck converter ICs from Global Foundries in July 2019. These ICs were packaged and characterized.

Bench equipment measurements showed good Buck converter line regulation and overall performance. The Buck converter IC band-gap reference (BGR), the test MUXs, the control loop amplifiers and the regulation subcircuits performed well. The band-gap reference gave a supply independent reference voltage of 1.32 V, with the bias supply range of 2 V to 3.5 V. The Buck converter inner current control-loop and outer voltage control loop functioned as designed. The regulated output voltage was 1.65 V and output ripple was around  $\pm 10$ mV. The load current was regulated at 42 mA with a 40 $\Omega$  internal load.

The task researchers developed methods for smallsignal LDO control-loop characterization. These methods are important for determining LDO stability and reliability. The safety of automobile brake control systems can be compromised by unstable compensation in the LDO control-loop. Reseachers developed small-signal test boards for the LDO test IC that enabled switching out control loop elements (capacitors and resistors).

Figure 1. The LDO control loop measurement schematic.

Bode 100 analyzer probes were placed across  $R_{bode}$  to determine the control-loop small-signal performance. For PSRR measurement, a test signal was injected at  $V_{in}$  through an injection transformer. LDO control-loop cutoff frequency measurements showed the ability to determine outlier values of  $C_{out}$ , the critical compensation capacitor. Work is continuing to translate the servo-loop technique to a loadboard circuit for ATE-based testing.

#### Keywords: Test, Analog, Power, LDO, Buck Converter

#### INDUSTRY INTERACTIONS

Texas Instruments

#### MAJOR PAPERS/PATENTS

[1] A. Tulsiram, and W. Eisenstadt, "In Situ DC Loop Gain and Stability Measurement of LDOs using a Nulling Op-Amp Servo Loop," Fourth ART Workshop, Washington, D.C., USA, November 14-15, 2019.

# TASK 2712.019, PRE-COMPUTED SECURITY PROTOCOLS FOR ENERGY HARVESTED IOT

### PATRICK SCHAUMONT, VIRGINIA TECH, SCHAUM@VT.EDU

#### SIGNIFICANCE AND OBJECTIVES

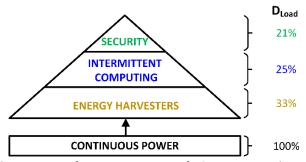

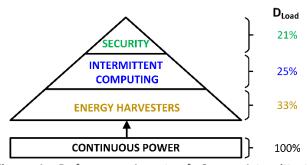

We optimize the latency and energy-efficiency of Internet security protocols in energy-harvesting IoT. An energy-harvesting IoT device has a limited and leaky energy-storage capacity. The energy must be used as soon as possible after harvesting. With pre-computing techniques, cryptographic applications can instantly use the harvested energy. Pre-computed results are stored efficiently and reliably in non-volatile memory and are used to improve latency. We demonstrate precomputed random-number generation and cryptographic keyexchange, which are part of Internet security protocols.

#### TECHNICAL APPROACH

The feasibility and efficiency of the proposed techniques will be evaluated through an end-to-end demonstrator with an energy-efficient micro-controller and with a wireless communication front-end. We develop techniques to spread out computations over time by reformulating cryptographic algorithms as capable of generating coupons, which are precomputed portions of the algorithm. We propose techniques for coupon generation and their secure storage in non-volatile, possibly off-chip memories. We also consider and optimize the impact of precomputed security protocols on the communication cost and the storage cost. We validate the proposed approach by constructing a prototype implementation on an energy-harvesting oriented microcontroller-based platform.

#### SUMMARY OF RESULTS

When a computing platform temporarily loses power, it stores its current state in a checkpoint, such that it can recover and continue execution at the point just before storing the checkpoint. A checkpoint also holds precomputed results (or coupons) to support the execution of a single cryptographic algorithm over multiple powerloss events. We performed a detailed security analysis of storing checkpoints in non-volatile memory. Also, a checkpoint also holds pre-computed results. We identify three possible scenarios that can threaten the security of the checkpointing process: a checkpoint may be snooped (eavesdropped upon), a checkpoint may be snooped (tampered), and a checkpoint may be replayed. Each of these attacks can lead to loss of information security on the IoT device, or loss of control.

Figure 1. Performance Impact of Secure Intermittent Computing for ECDH.

We have evaluated the overhead of our proposed Secure Intermittent Computing protocol (SICP) for the case of cryptographic key exchange (ECDH). The prototype is constructed for a Texas Instruments MSP430FR5994 microcontroller that is performing key exchange under energy harvesting. The results are shown as a relative overhead compared to a continuously powered design. We measured the continuous ECDH operation to consume 6.3 mW and we assumed a 2 mW kinetic energy harvester, yielding a 33% duty cycle under intermittent operation. This duty cycle would imply key exchange takes 3 times as long under energy harvesting operation. The selected p160 curve for ECDH uses a 1211-byte checkpoint which must be stored and retrieved, and which reduces the duty cycle further to 25%. Implementing secure checkpoints, as enabled using SICP, adds additional overhead of encryption, and reduces the operation duty cycle to 21%. Hence, we conclude that the overhead of secure checkpointing on a realistic cryptographic protocol increases from 3x (only energy harvesting) to 5x (including secure checkpointing).

We have summarized out conclusions of the project in a forthcoming journal paper [1].

**Keywords:** cryptography, energy-harvesting, NVM applications, intermittent computing, MSP430

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] A. S. Krishnan, C. Suslowicz, P. Schaumont, "Secure and Stateful Power Transitions in Embedded Systems," IEEE Transactions on VLSI Systems, under review.

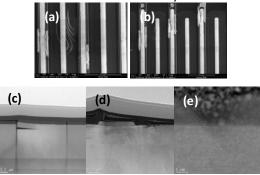

## TASK 2712.021, DISTRIBUTED SILICON CIRCUITS AND SENSORS IN 3D-PRINTED SYSTEMS FOR WEARABLE IOT SENSORS MATTHEW L. JOHNSTON, OREGON STATE UNIVERSITY, JOHNSTON@OREGONSTATE.EDU YIĞIT MENGÜÇ, OREGON STATE UNIVERSITY

#### SIGNIFICANCE AND OBJECTIVES

There is an emerging set of applications that require stretchable, compliant electronics – including wearable devices, instrumented fabrics, and soft robots with distributed sensors and computation. In this project, we are working to demonstrate a fundamentally new method for the fabrication of stretchable, 3D-printed objects containing distributed sensors and silicon ICs.

#### **TECHNICAL APPROACH**

Developing stretchable electronics faces two primary challenges: integration of active semiconductor devices in elastic substrates and providing stretchable, conductive interconnects. In this project, we combine 3D printing of liquid metal materials and silicone rubber with PCB fabrication techniques to build solid 3D objects with electronic components distributed throughout. Silicon integrated circuits, used for computation, sensing, and actuation will be connected through liquid metal conductors confined to 3D microfluidic channels. Through additive, layer-by-layer construction, electronic devices can be inserted and connected throughout the 3D structure. We will also develop compact models for the interconnects, which will be used to design adaptable front-end circuits for stretchable interconnect interfaces.

#### SUMMARY OF RESULTS

Over the course of this project, we have demonstrated progress (Fig. 1) in printing multi-layer stretchable circuits using discrete components, extended strain testing of liquid metal paste material, and developed a compact modeling framework for stretchable interconnects. Specific outcomes have included:

- Demonstrated printing of sensors and analog and digital interconnects using discrete active and passive components [1,2].

- Extended testing of stretchable interconnects, demonstrating <5% change in resistance over 100,000 stretch cycles at 50% strain (1.5X) [4].

- Established a compact modeling framework for Cadence-compatible simulation of stretchable interconnects under static and dynamic strain [3].

- Printed antenna structures were developed, and a 2.4GHz liquid metal paste antenna structure was fabricated for future integration into stretchable circuits for wireless communication.

Figure 1. Printed stretchable circuits (top) with active and passive components [1]; 100,000 cycle strain data (bottom).

**Keywords:** Stretchable electronics; 3D printing; wearable devices; packaging; sensor interfaces

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, IBM

#### MAJOR PAPERS/PATENTS

[1] C. Votzke, U. Daalkhaijav, Y. Mengüç, and M.L. Johnston, "3D-printed liquid metal interconnects for stretchable electronics," *IEEE Sensors Journal*, vol. 19, no. 10, pp. 3832 - 3840, 2019.

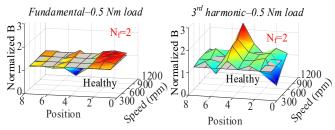

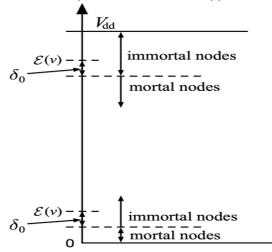

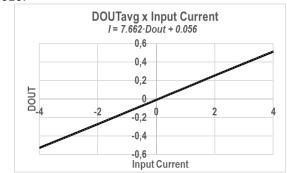

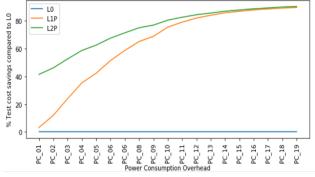

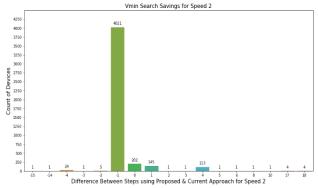

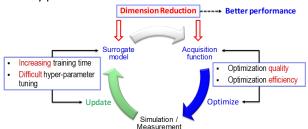

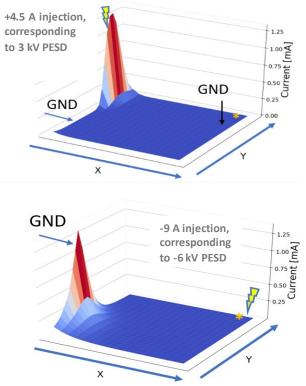

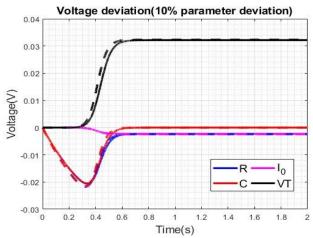

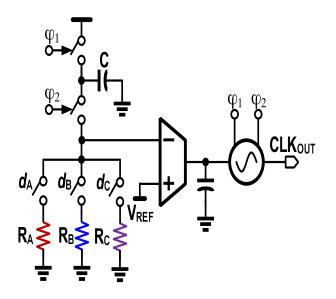

[2] C. Votzke, U. Daalkhaijav, Y. Mengüç, and M.L. Johnston, "Highly-stretchable biomechanical strain sensor using printed liquid metal paste," 2018 BioCAS, Cleveland, OH, Oct. 2018.