# TEXAS ANALOG CENTER OF EXCELLENCE Annual Report 2016 – 2017

# **TxACE MISSION**

The Texas Analog Center of Excellence seeks to create fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

# **TxACE THRUSTS**

Safety, Security and Health Care

Energy Efficiency

Fundamental Analog Circuits

# TxACE 2016-2017 ANNUAL REPORT

The Texas Analog Center of Excellence (TxACE), located at the University of Texas at Dallas is the largest analog research center based in an academic institution. Analog and mixed signal integrated circuits engineering is both a major opportunity and challenge. Analog circuitry is a critical component of nearly every product of the ~\$350 billion per year integrated circuits industry, as a part of sensing, actuation, communication, power management and others. Digital integrated circuits such as microprocessors, logic circuits and memories are now integrating analog functions such as input/output circuits, phase locked loops, temperature sensors and power management circuits. It is also common to find microcontrollers with multiple analog-to-digital and digital-to-analog converters. These circuitries impact almost all aspect of modern life: safety security, health care, transportation, energy, entertainment and others.

Creation of advanced analog and mixed signal circuits and systems depends on the availability of engineering talent for analog research and development. TxACE was established to help translate the opportunity into economic benefits by overcoming the challenge and meeting the need. TxACE was established through a collaboration of the state of Texas, Texas Instruments, the Semiconductor Research Corporation, the University of Texas System, and The University of Texas at Dallas.

The research tasks are organized into three research thrust areas: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog. The scope of investigation extends from circuits operating at dc through terahertz, data converters that sample at a few samples/sec to 10's of Giga-samples/sec, AC-to-DC and CD-to-AC converters working at  $\mu$ W to Watts, energy harvesting circuits, sensors and many more. Significant improvements to existing mixed signal systems and new applications have been made and continued to be anticipated. Students who have been exposed to hands-on innovative research are forming the leading edge of analog talent flow into the industry. Close collaboration with and responsiveness to industry needs provide focus to the educational experience.

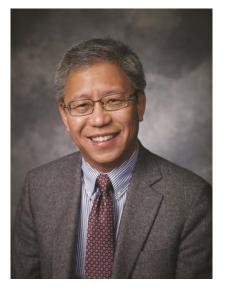

#### DIRECTOR'S MESSAGE

The Texas Analog Center of Excellence (TxACE) is leading analog research and education. I am excited to report that the Center has been renewed for another three years and is starting its 10<sup>th</sup> year of operation this fall. I would like to thank the Semiconductor Research Corporation, Texas Instruments, University of Texas at Dallas and University of Texas System for their confidence and continuing support.

Last year, TxACE researchers published 28 journal and 48 conference papers. We also filed 4 patents and 1 invention disclosure. Twenty-three Ph.D. and four M.S. students have completed their degree program. The Center funded 59 research tasks led by 43 principal investigators at 20 academic institutions, including one international university. Five universities (SMU, Rice, Texas A&M, UT Austin, UT Dallas) were from the state of Texas. The Center supported 132 graduate and undergraduate students.

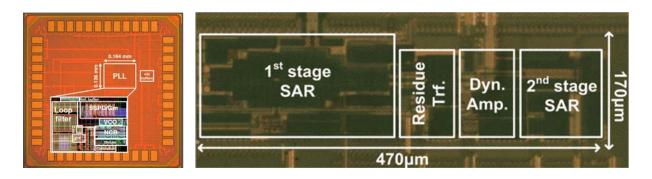

The Center accomplished much. As always, there are too many to list all here. A selected list includes demonstrations of a RISC-V system-on-chip with integrated voltage regulation and power management implemented in 28-nm FD-SOI with a total system efficiency of 41.8 double-precision GFLOPS/W, a 12-b 330MS/s single-channel pipelined-SAR ADC employing a PVTstabilized dynamic amplifier as the residue amplifier instead of power hungry opamps that achieves an FoM of 9.5fJ per conversion, and a resonant-based circuit architecture for power isolation with the peak power efficiency of 50.7% and the maximum output power of 62mW, which achieves a 4X efficiency and a 3X power delivery improvement.

The TxACE laboratory is continuing to help advance integrated circuit research by making its instruments and expertise available to researchers and our industrial partners all over the world.

I would like to thank the students, principal investigators and staff for their efforts, and UT Dallas, the University of Texas System, TI, and SRC, as well as many friends of TxACE all over the world for their generous support. As we celebrate our 10<sup>th</sup> year, I look forward to another year of working with the TxACE team to make our world better through our research, education and innovation.

Kenneth K. O, Director TxACE Texas Instruments Distinguished University Chair Professor The University of Texas at Dallas

### **BACKGROUND & VISION**

The \$350 billion per year integrated circuits industry is evolving into an analog/digital mixed signal industry. Analog circuits are providing or supporting critical functions such as sensing, actuation, communication, power management and others. These circuits impact almost all aspect of modern life including safety, security, health care, transportation, energy, and entertainment. To lead this change, in particular to lead analog and mixed signal technology education, research, commercialization, manufacturing, and job creation, the Texas Analog Center of Excellence was announced by Texas Governor Rick Perry in October 2008 as a collaboration of the Semiconductor Research Corporation, state of Texas through its Texas Emerging Technology Fund, Texas Instruments Inc., University of Texas system and University of Texas at Dallas. The Center seeks to accomplish the objectives by creating fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, healthcare, and public safety and security as well as by improving the research and educational infrastructure.

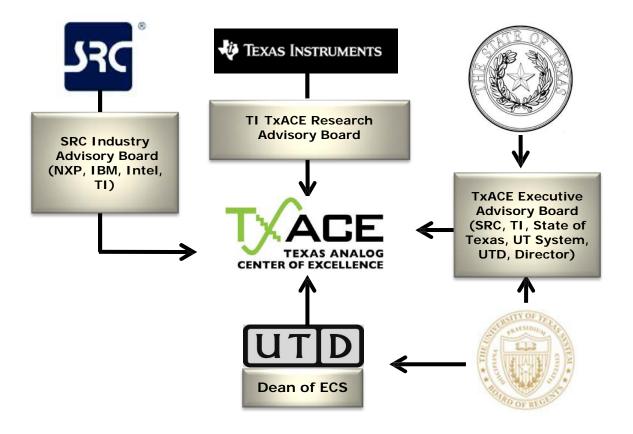

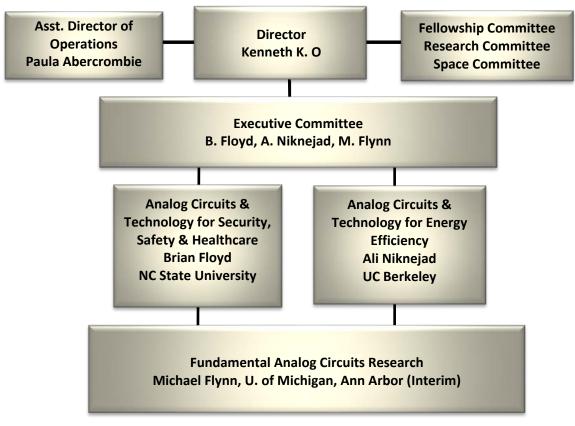

Figure 1. TxACE organization relative to the sponsoring collaboration

## **CENTER ORGANIZATION**

The Texas Analog Center of Excellence is guided by agreements established with the Center sponsors. Members of the industrial advisory boards identify the research needs and select research tasks in consultation with the Center leadership. Figure 1 diagrams the relationship of TxACE to the members of the sponsoring collaboration.

# The internal organization of the Center is structured to flexibly perform the research mission while fully embracing the educational missions of the Universities.

Figure 2 shows the center management structure. The TxACE Director is Professor Kenneth O. The research is arranged into three thrusts that comply with the center mission: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog Research. The third thrust consists of vital research that cuts across the first two research thrusts. The thrust leaders are Prof. Brian A. Floyd of North Carolina State University for safety, security and health care, and Prof. Ali Niknejad of the University of California, Berkeley for energy efficiency. The interim leader for fundamental analog is Prof. Michael Flynn of University of Michigan, Ann Arbor. The thrust leaders form the executive committee. The committee, along with the director, forms the leadership team that works to improve the research productivity by increasing collaboration, better leveraging the diverse capabilities of principle investigators of the Center, and lowering research barriers. The leadership team also identifies new research opportunities for consideration by the Industrial Advisory Boards.

Figure 2. TxACE organization for management of research

## PUBLIC SAFETY, SECURITY AND HEALTH CARE

### (Thrust leader: Brian Floyd, NC State University)

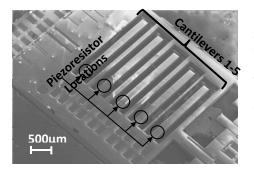

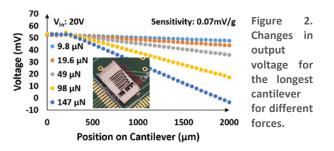

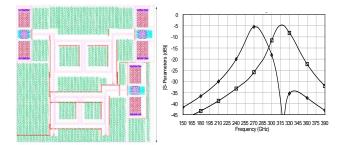

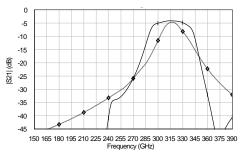

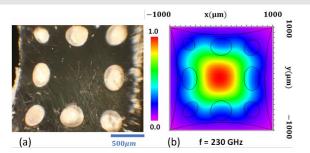

TxACE is developing analog technology that enhances public safety and security, and health care. The projects are intended to enable a new generation of devices that can scan for harmful substances by researching 200-300 GHz silicon ICs for use in spectrometers as well as a CO<sub>2</sub> sensor. The ICs and CO<sub>2</sub> sensor can also be used to analyze breaths for medical applications. The thrust is also working to significantly reduce the cost of millimeter wave imaging and on-vehicle radar technology for automotive safety by researching circuit techniques that can improve manufacturing, and simplify test and packaging, as well as signal processing techniques that reduce system complexity. Lastly, this thrust is investigating vibration sensors.

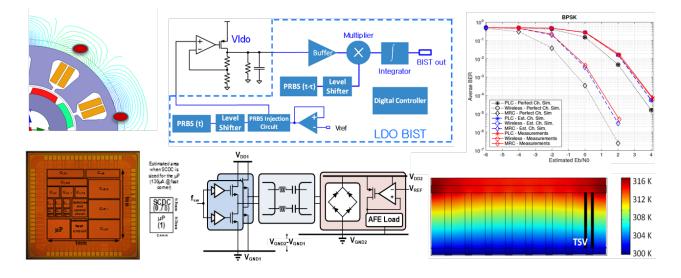

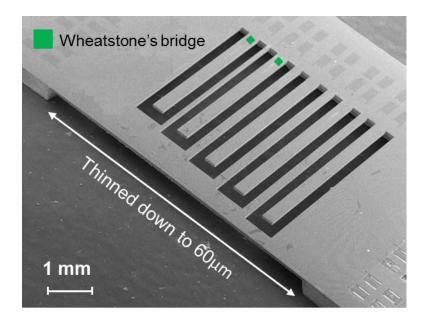

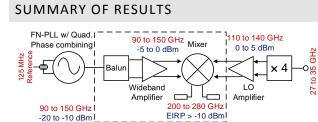

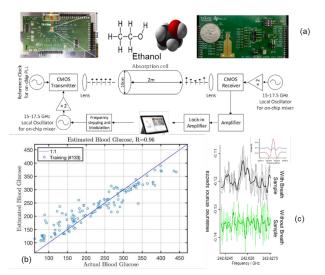

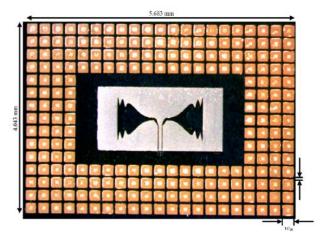

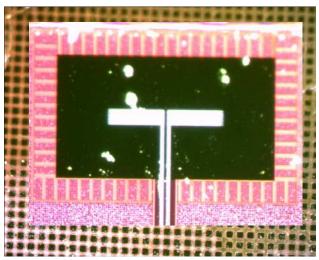

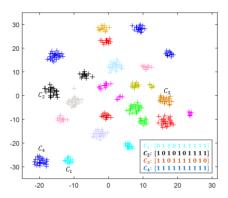

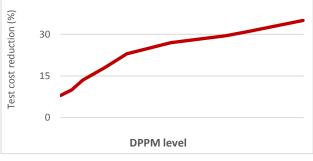

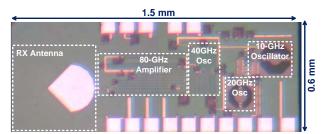

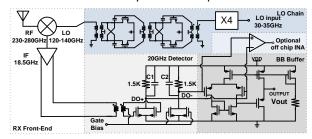

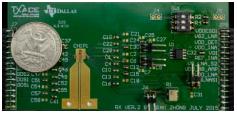

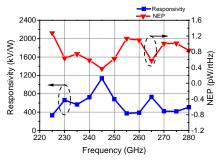

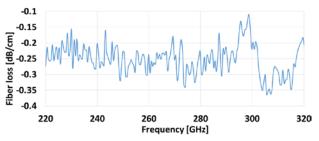

Figure 3. (Top left) 200-260 GHz CMOS transmitter and receiver for rotational spectroscopy (K. O, W. Choi, UT-Dallas), (Top right) Injection-locked receiver for synchronization of widely spaced imaging array (A. Babakhani, Rice U.), (Bottom left) Vibration sensor compatible with conventional silicon IC and packaging technologies (S. Pourkamali, UT Dallas), (Bottom left center) Automotive radar imaging (M. Torlak, UT-Dallas), (Bottom right center) Projected e-test space, where each point represents a wafer. A proper test flow to each process signature of each wafer is assigned to maximize the test cost reduction while maintaining the test escape rate below a target level. (Y. Makris, UT-Dallas), (Bottom right) Magnitude of field inside a dielectric waveguide (D. MacFarlane, SMU).

### **ENERGY EFFICIENCY**

(Thrust leader: Ali Niknejad, UC Berkeley)

TxACE is committed to alleviate the global energy problem by improving the energy efficiency of electronic systems as well as by developing analog technologies that can make energy generation and distribution more efficient. The Center is also working to energize and power long-lasting in-situ microscale devices such as wireless microsensors, biomedical implants, and portable microelectronics.

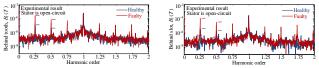

Figure 4. (Top left) Simulated flux leakage in a motor (B. Akin, UT-Dallas), (Top center) Dynamic BIST for LDO's (S. Ozev, Arizona State U.), (Top right) BER versus SNR for PLC/Wireless receiver combining techniques based on maximal-ratio-combining that take into account the impulsive nature of noise on the two links (N. Al-Dhahir, UT-Dallas, B. Evans, UT-Austin), (Bottom left) Microprocessor and switched-capacitor DC-DC converter power management unit based on direct error regulation (M. Seok, Columbia U.), (Bottom center) Resonant converter for isolated power transfer (B. Ma, UT-Dallas), (Bottom right) Simulated cross-sectional temperature distribution in a 8-row TSV arrangement (J. Lee, N. Bagherzadeh, UC-Irvine).

## FUNDAMENTAL ANALOG CIRCUITS RESEARCH

(Thrust leader: U. of Michigan Ann Arbor)

Research in this thrust focuses on cross-cutting areas in Analog Circuits which impact all of the TxACE application areas (Energy Efficiency, Public Safety and Security, Health Care). The list of research includes design of a wide variety of analog-to-digital converters, communication links, temperature sensors and I/O circuits, development of CAD tools, and testing of integrated circuits.

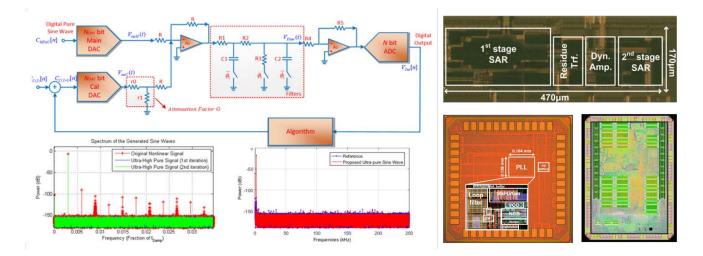

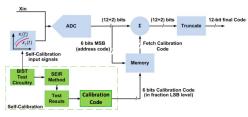

Figure 5. (Left) Low cost ultra-pure sine wave generation with self-calibration. (D. Chen, R. Geiger, Iowa State), (Top right), 12-b 330MS/s single-channel pipelined-SAR ADC (Y. Chiu, UT Dallas), (Bottom center) 2-2.8GHz 65-nm CMOS ring oscillator PLL (P. Kinget, Columbia), (Bottom right) DLL-based clock generation, with phase picking controlled by tunable replica circuits (B. Nikolic).

## **TXACE ANALOG RESEARCH FACILITY**

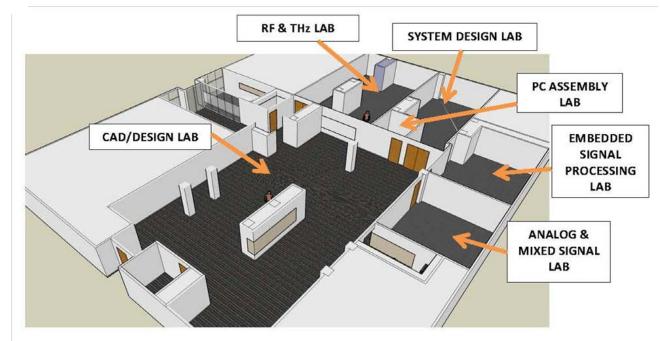

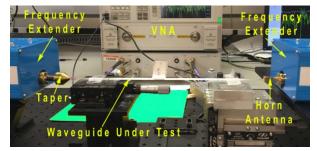

The centralized group of laboratories of the Texas Analog Center of Excellence dedicated to analog engineering research and training occupies a ~8000 ft<sup>2</sup> area on the 3rd floor of the Engineering and Computer Science North building (Figure 6). The facility includes RF and THz, Integrated System Design, Embedded Signal Processing, and Analog & Mixed Signal laboratories as well as CAD/Design laboratory structured to promote collaborative research. The unique instrumentation capability includes network analyses and linearity measurements up to 325 GHz, spectrum analysis up to 120 THz, and cryo-measurements down to 2°K. The Center also added a pulsed multiple harmonic load and source pull measurement set up (up to 60 GHz for the third harmonic) and a 325-GHz antenna measurement set up. The close proximity of researchers in an open layout enables natural interaction and compels sharing of knowledge and instrumentation among the students and faculty. The TxACE analog research facility is one of the best equipped electronics laboratories. The laboratory is available for use by TxACE researchers and industrial partners all over the world.

Figure 6. TxACE Analog Research Facility

## **RESEARCH PROJECTS AND INVESTIGATORS**

The Texas Analog Center of Excellence (TxACE) is the largest university analog technology center in the world. Table 1 lists the current principal investigators of the 59 tasks from 20 academic institutions funded by TxACE. Five universities (Rice, SMU, Texas A&M, UT Austin, UT Dallas) are from the state of Texas. Fourteen are from outside of Texas. One (Seoul National University) (Figure 7) is from outside of the US. Of the 43 investigators, 18 are from Texas. During the past year, the Center supported 104 Ph.D., 16 M.S., and 12 B.S. students. Twenty-three Ph.D. and four M.S. degrees were awarded to the TxACE students.

| Investigator  | Institution  | Investigator    | Institution  | Investigator    | Institution   |

|---------------|--------------|-----------------|--------------|-----------------|---------------|

| B. Akin       | UT Dallas    | R. Harjani      | U Minnesota  | A. Niknejad     | UC Berkeley   |

| N. Al-Dhahir  | UT Dallas    | R. Henderson    | UT Dallas    | B. Nikolić      | UC Berkeley   |

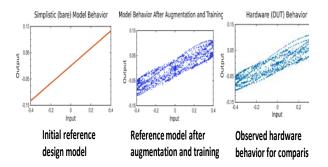

| A. Babakhani  | Rice U       | C. Kim          | U Minnesota  | К. О            | UT Dallas     |

| D. Blaauw     | U Michigan   | J. Kim          | Seoul Nat.   | S. Ozev         | Arizona State |

| A. Chatterjee | Georgia Tech | P. Kinget       | Columbia     | S. Palermo      | Texas A&M     |

| D. Chen       | Iowa State   | H. Lee          | UT Dallas    | S. Pourkamali   | UT Dallas     |

| Z. Chen       | U Arkansas   | J. Lee          | UC Irvine    | S. Prasad       | UT Dallas     |

| Y. Chiu       | UT Dallas    | M. Lee          | UT Dallas    | A. Raychowdhury | Georgia Tech  |

| W. Choi       | UT Dallas    | P. Li           | Texas A&M    | E. Rosenbaum    | UIUC          |

| F. De Lucia   | Ohio State   | D. Ma           | UT Dallas    | V. Sathe        | U Washington  |

| W. Eisenstadt | U Florida    | D. MacFarlane   | SMU          | M. Seok         | Columbia      |

| B. Evans      | UT Austin    | N. Maghari      | U Florida    | G. Temes        | Oregon State  |

| M. Flynn      | U Michigan   | Y. Makris       | UT Dallas    | M. Torlak       | UT Dallas     |

| R. Geiger     | Iowa State   | UK. Moon        | Oregon State |                 |               |

| P. Hanumolu   | UIUC         | S. Mukhopadhyay | Georgia Tech |                 |               |

#### Table 1. Principal Investigators (September 2016 through August 2017)

Figure 7. Member Institutions of Texas Analog Center of Excellence

## **SUMMARY OF RESEARCH PROJECTS**

The 59 research projects funded through TxACE during 2016-2017 are listed in Table 2 below by the Semiconductor Research Corporation task identification number.

# Table 2: Funded research projects at TxACE by SRC task identification number (FA: Fundamental Analog, EE: Energy Efficiency, SSH: Safety, Security and Health Care)

|    | TASK     | THRUST | TITLE                                                                                                                       | TASK LEADER              | INSTITUTION          |

|----|----------|--------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|

| 1  | 1836.096 | FA     | Mixed-Signal Design Centering in Deeply<br>Scaled Technologies                                                              | Nikolić, Borivoje        | UC Berkeley          |

| 2  | 1836.110 | EE     | Distributed Power Delivery Architecture for 2D<br>and 3D Integrated Circuits                                                | Mukhopadhyay,<br>Saibal  | Georgia Tech         |

| 3  | 1836.111 | FA     | Advanced ADC-Based Serial Link Receiver<br>Architectures                                                                    | Palermo, Samuel          | Texas A&M            |

| 4  | 1836.112 | EE     | Shortstop: Fast Power Supply Boosting for<br>Energy-Efficient, High-Performance Processors                                  | Blaauw, David            | Univ. of<br>Michigan |

| 5  | 1836.117 | FA     | Performance and Reliability Enhancement of<br>Embedded ADCS with Value-Added BIST                                           | Geiger, Randall          | Iowa State           |

| 6  | 1836.119 | SSH    | Demonstration of 180-300 GHz Transmitter for<br>Rotational Spectroscopy                                                     | O, Kenneth               | UT Dallas            |

| 7  | 1836.120 | SSH    | Evaluation of Frequency and Noise<br>Performance of CMOS 180-300 GHz<br>Spectrometer Transmitter and Receiver<br>Components | Lee, Mark                | UT Dallas            |

| 8  | 1836.122 | SSH    | On-Chip Integration Techniques for 180-300<br>GHz Spectrometers                                                             | Henderson,<br>Rashaunda  | UT Dallas            |

| 9  | 1836.124 | EE     | Digitally-Enhanced Clocking Strategies to<br>Improve Energy-Efficiency of Serial Links                                      | Hanumolu, Pavan<br>Kumar | UIUC                 |

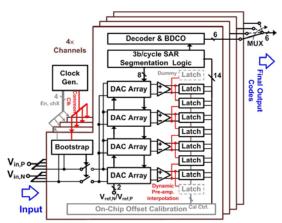

| 10 | 1836.125 | FA     | 10GS/s+ Resolution-Scalable (4-7bits) ADCs                                                                                  | Flynn, Michael           | Univ. of<br>Michigan |

| 11 | 1836.126 | SSH    | Design Spin Reduction via Integrated THz<br>Design: Applications, Physics, and System<br>Engineering                        | De Lucia, Frank          | Ohio State           |

| 12 | 1836.127 | FA     | Precision Test without Precision Instruments –<br>A Necessity for Future On-Chip Self-Test and<br>Self Healing              | Chen, Degang             | Iowa State           |

| 13 | 1836.128 | FA     | Statistical Analog Design Property Checking                                                                                 | Li, Peng                 | Texas A&M            |

| 14 | 1836.129 | FA     | Energy-Efficient Digitally-Enhanced Rapid<br>ON/OFF Links in Nano-scale CMOS                                                | Hanumolu, Pavan<br>Kumar | UIUC                 |

| 15 | 1836.130 | EE     | Built-In Self-Test Techniques for Test,<br>Calibration, and Trimming of Power<br>Management Units: PMU-BIST                 | Ozev, Sule               | Arizona State        |

| 16 | 1836.131 | SSH    | Process Variation Anatomy: A Statistical Nexus<br>Between Design, Manufacturing, and Yield                                  | Makris, Yiorgos          | UT Dallas            |

|    | Task     | Thrust | Title                                                                                                                  | Task Leader             | Institution             |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|

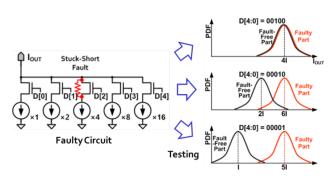

| 17 | 1836.132 | FA     | Fault Coverage Analysis of Analog/Mixed-Signal<br>Tests Based on Statistical Dissimilarity                             | Kim, Jaeha              | Seoul National<br>Univ. |

| 18 | 1836.133 | EE     | Energy-Efficient Signal Processing Techniques for<br>Smart Grid Heterogeneous Communications<br>Networks               | Al-Dhahir, Naofal       | UT Dallas               |

| 19 | 1836.134 | FA     | Hybrid Two-Step PLLs for Digital SoCs in Nanoscale<br>CMOS                                                             | Kinget, Peter           | Columbia                |

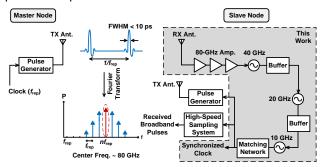

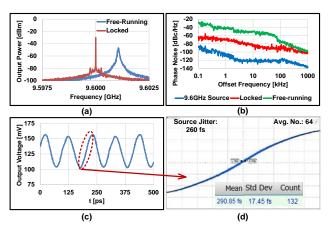

| 20 | 1836.135 | SSH    | Sub-Picosecond Synchronization of Widely Spaced<br>Imaging Arrays                                                      | Babakhani, Aydin        | Rice Univ.              |

| 21 | 1836.136 | FA     | Injection-Locked Ring Oscillators for Clock<br>Distribution in Manycore Processors                                     | Nikolić, Borivoje       | UC Berkeley             |

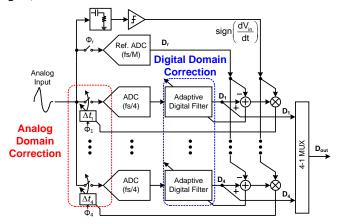

| 22 | 1836.137 | FA     | 50GS/s and Beyond Frequency-interleaved Energy-<br>Efficient ADCs                                                      | Niknejad, Ali           | UC Berkeley             |

| 23 | 1836.138 | EE     | Micro-Power Analog-to-Digital Data Converters                                                                          | Temes, Gabor            | Oregon State<br>Univ.   |

| 24 | 1836.139 | EE     | Enabling Fully-Integrated VHF CLK-Sync Multiphase<br>Switching Regulators on Silicon                                   | Ma, Dongsheng           | UT Dallas               |

| 25 | 1836.140 | EE     | Embedded & Adaptive Voltage Regulators with<br>Proactive Noise Reduction for Digital Loads Under<br>Wide Dynamic Range | Raychowdhury,<br>Arijit | Georgia Tech            |

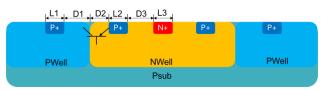

| 26 | 1836.141 | FA     | IC Design for Resilience Against System-Level ESD                                                                      | Rosenbaum, Elyse        | UIUC                    |

| 27 | 1836.142 | EE     | Low Power Applications of FRAM                                                                                         | Blaauw, David           | Univ. of<br>Michigan    |

| 28 | 1836.143 | EE     | Design Techniques for Modulation-Agile and<br>Energy-Efficient 60+Gb/s Receiver Front-Ends                             | Palermo, Samuel         | Texas A&M               |

| 29 | 1836.144 | EE     | High-efficiency High-voltage Power Converters                                                                          | Lee, Hoi                | UT Dallas               |

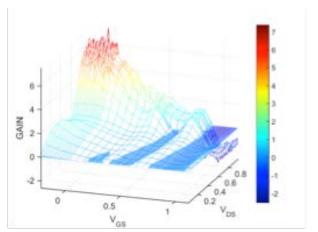

| 30 | 1836.145 | FA     | RF and Mixed Signal Quantum CMOS Devices and<br>Circuits                                                               | Lee, Mark<br>Chiu, Yun  | UT Dallas               |

| 31 | 1836.146 | EE     | On-Chip AC-DC Power Conversion with Ground<br>Disturbance Shielding for Environmental Sensing<br>Applications          | Ma, Dongsheng           | UT Dallas               |

| 32 | 1836.147 | SSH    | Demonstration of 180-300 GHz Receiver for<br>Rotational Spectroscopy                                                   | Choi, Wooyeol           | UT Dallas               |

| 33 | 1836.148 | FA     | 50GSPS+ TI Hybrid SAR ADC Array with<br>Comprehensive DDI Calibration                                                  | Chiu, Yun               | UT Dallas               |

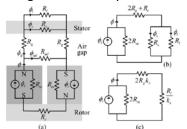

| 34 | 1836.149 | EE     | Condition Monitoring of PM/IPM Motors through<br>Axial/Radial Leakage Flux                                             | Akin, Bilal             | UT Dallas               |

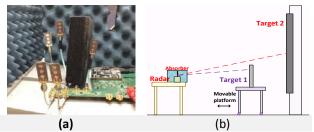

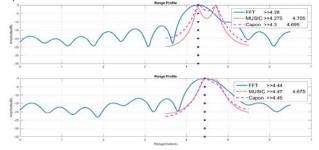

| 35 | 1836.150 | SSH    | Robust High Resolution Techniques for Millimeter<br>Wave Radars in Complex Environments                                | Torlak, Murat           | UT Dallas               |

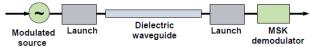

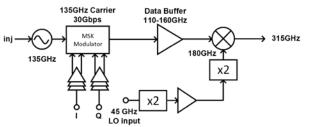

| 36 | 1836.152 | SSH    | Feasibility of CMOS Transmitter and Receiver for<br>500-Gbps Communication over Dielectric<br>Waveguide                | O, Kenneth K.           | UT Dallas               |

| 37 | 1836.153 | EE     | High-Speed Compact Power Supplies For Ultra-<br>Low-Power Wireless Sensor Applications                                 | Ma, Dongsheng           | UT Dallas               |

| 38 | 1836.154 | EE     | State of The Health (SOH) for IGBTS: Incipient Fault<br>Characterization and Degradation Monitoring                    | Akin, Bilal             | UT Dallas               |

|    | Task     | Thrust | Title                                                                                                                         | Task Leader              | Institution   |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|

| 39 | 1836.155 | SSH    | Development of Wideband Vibration Sensors<br>Based On Existing Process Platforms                                              | Pourkamali,<br>Siavash   | UT Dallas     |

| 40 | 1836.156 | SSH    | Transition Design for High Data Rate Links at<br>Submillimeter Wave Frequencies                                               | Henderson,<br>Rashaunda  | UT Dallas     |

| 41 | 1836.157 | FA     | CMOS GSPS 12-Bit SAR ADC Array With On-Chip<br>Reference Buffers                                                              | Chiu, Yun                | UT Dallas     |

| 42 | 1836.158 | SSH    | Development of Dielectric Waveguides for THz<br>Radiation Applications                                                        | Macfarlane,<br>Duncan    | SMU           |

| 43 | 1836.159 | SSH    | Performance of Carbon Dioxide (CO(2)) Gas<br>Sensors                                                                          | Prasad, Shalini          | UT Dallas     |

| 44 | 2712.002 | EE     | On-line Self-Testing and Self-Tuning of Integrated<br>Voltage Regulators                                                      | Mukhopadhyay,<br>Saibal  | Georgia Tech  |

| 45 | 2712.003 | FA     | Multi-Modal BIST Design and Test Metrics<br>Evaluation for Analog/RF Circuits                                                 | Ozev, Sule               | Arizona State |

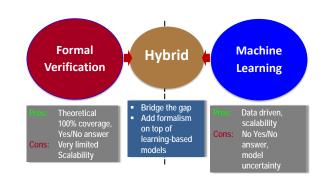

| 46 | 2712.004 | FA     | Hierarchical Analog and Mixed-Signal Verification<br>Using Hybrid Formal and Machine Learning<br>Techniques                   | Li, Peng                 | Texas A&M     |

| 47 | 2712.005 | FA     | Automated Cross-Level Validation and Debug of<br>Mixed-Signal Systems in Top-Down Design: From<br>Pre-Silicon to Post-Silicon | Chatterjee, Abhijit      | Georgia Tech  |

| 48 | 2712.006 | EE     | Robust, Efficient All-Digital SIMO Converters for<br>Future SOC Domains                                                       | Sathe, Visvesh           | U Washington  |

| 49 | 2712.007 | FA     | High-Resolution Low-Voltage Hybrid ADCs for<br>Sensor Interfaces                                                              | Flynn, Michael P.        | U Michigan    |

| 50 | 2712.008 | EE     | Direct-Battery-to-Silicon Power Transfer in<br>Advanced Nanometer CMOS                                                        | Harjani, Ramesh          | U Minnesota   |

| 51 | 2713.009 | EE     | Low Power Area Efficient Flexible-rate Energy<br>Proportional Serial Link Transceivers                                        | Hanumolu, Pavan<br>Kumar | UIUC          |

| 52 | 2712.010 | FA     | Ringamp-assisted Circuits/Techniques and Next-<br>generation Ringamps                                                         | Moon, Un-Ku              | Oregon State  |

| 53 | 2712.011 | FA     | Robust Reliable and Practical High Performance<br>References in Advanced Technologies                                         | Geiger, Randall L.       | Iowa State    |

| 54 | 2712.012 | EE     | EDAC and DC-DC-Converter Co-Design for<br>Addressing Robustness Challenges in Emerging<br>Architectures                       | Seok, Mingoo             | Columbia      |

| 55 | 2712.014 | FA     | Leveraging CMOS Scaling in High Performance<br>ADCS                                                                           | Maghari, Nima            | U Florida     |

| 56 | 2712.015 | FA     | Area-Efficient On-Chip System-Level IEC ESD<br>Protection for High Speed Interface ICs                                        | Chen, Zhong              | U Arkansas    |

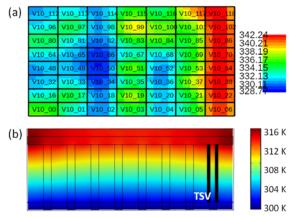

| 57 | 2712.016 | EE     | 3D IC Thermal Management Based on TSV<br>Placement Optimization and Novel Materials                                           | Lee, Jaeho               | UC Irvine     |

| 58 | 2712.017 | FA     | Mitigating Reliability Issues in Analog Circuits                                                                              | Kim, Chris H.            | U Minnesota   |

| 59 | 2712.018 | EE     | Test Techniques to Approach Several Defect-per-<br>billion for Power ICs                                                      | Eisenstadt,<br>William   | U Florida     |

## ACCOMPLISHMENTS

In the past year, TxACE has made significant research progress. Table 3 summarizes the number of publications and inventions resulting from the TxACE research during May 2016 to April 2017, while Table 4 lists the major research accomplishments for the Center during the period. The TxACE researchers have published 48 conference papers and 29 journal papers. They have also filed one invention disclosure and 4 patents. The list of publications is included as Appendix I. Following the tabulation, brief summaries of each project are provided.

| Conference Papers | Journal Papers | Invention Disclosures | Patents Filed | Patents Granted |

|-------------------|----------------|-----------------------|---------------|-----------------|

| 48                | 28             | 1                     | 4             | 0               |

### Table 3. TxACE number of publications (May 2016 through April 2017)

| Category                            | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fundamental<br>Analog<br>(Circuits) | A RISC-V system-on-chip with integrated voltage regulation and power management is implemented in 28-nm FD-SOI. A fully integrated switched-capacitor DC-DC converter, coupled with an adaptive clocking system, achieves 82-89% system conversion efficiency across a wide operating range, yielding a total system efficiency of 41.8 double-precision GFLOPS/W. (1836.136, PI: B. Nikolic, UC-Berkeley)                                                                                                                                                                                                                                    |

| Fundamental<br>Analog<br>(Circuits) | A 12-b 330MS/s single-channel pipelined-SAR ADC employs a PVT-stabilized dynamic amplifier<br>as the residue amplifier instead of opamp-based residue amplifiers that consume significant<br>amounts of power due to stringent settling speed and accuracy requirements. The ADC<br>fabricated in 65-nm CMOS with a core area of 0.08mm <sup>2</sup> achieves an FoM of 9.5fJ per<br>conversion. The measured DNL and INL are +0.67/-0.56LSB and +0.7/-0.8LSB, respectively. The<br>measured SNDR remains above 60dB even with a 500-MHz input. (1836.157, PI: Y. Chiu, UT-                                                                   |

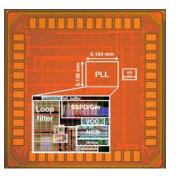

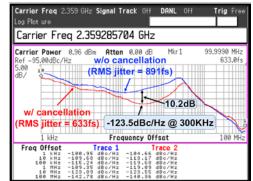

| Fundamental<br>Analog<br>(Circuits) | A 2-2.8GHz 65-nm CMOS ring oscillator PLL occupies an active area of 0.022 mm <sup>2</sup> , consumes 5.86mW, and achieves a 633fs RMS jitter at 2.36 GHz and an FOM <sub>jitter</sub> of -236 dB. It implements a low-overhead feed-forward phase and supply-noise cancellation scheme by leveraging the noise extraction inherently done by the sub-sampling phase detector. Cancellation reduces the jitter by 1.4X, the phase noise by 10.2dB to -123.5dBc/Hz at a 300KHz offset, and the ring oscillator supply sensitivity by 19.5dB for a 1-mV <sub>p-p</sub> 100KHz supply noise tone. (1836.134, PI: P. Kinget, Columbia University) |

| Energy<br>Efficiency<br>(Circuits)  | High-speed serial link receiver design and modeling techniques are proposed to significantly<br>improve interconnect bandwidth density in an energy-efficient manner. A statistical link<br>modeling tool was utilized to investigate the optimal equalization partitioning and<br>modulation format for 60+Gb/s signaling environments. A dual-mode NRZ/PAM4 SerDes<br>was implemented in GP 65-nm CMOS and achieved 16Gb/s NRZ and 32Gb/s PAM4 operation<br>at 10.9 and 5.5mW/Gb/s, respectively. (1836.143, PI: S. Palermo, Texas A&M University)                                                                                          |

#### Table 4. Major TxACE Research Accomplishments (May 2016 through April 2017)

| Category                                            | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy<br>Efficiency<br>(Circuits)                  | Capacitive isolation is used to eliminate the bulky magnetics for highly power efficient on-<br>silicon AC-DC power conversion for environmental sensor applications that is resilient to<br>ground voltage disturbance. However, the low density on-chip capacitor and large parasitics<br>limit the output power level and efficiency. A resonant-based circuit architecture for power<br>isolation with the peak power efficiency of 50.7% and the maximum output power of 62mW<br>is demonstrated. This design achieves a 4X efficiency and a 3X power delivery improvement<br>over the prior art. (1836.146, PI: Brian Ma, UT-Dallas) |

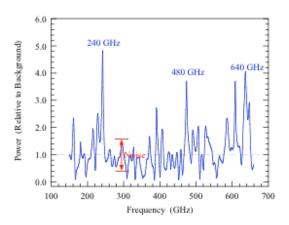

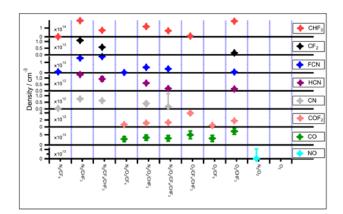

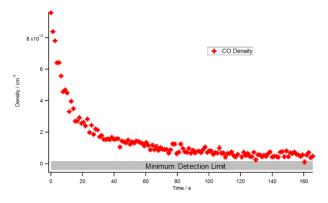

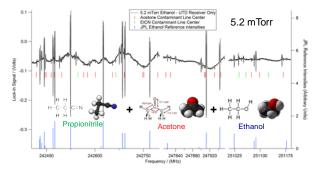

| Safety,<br>Security and<br>Health Care<br>(Systems) | Terahertz spectrometers can be used for a variety of applications including process monitoring<br>and gas detection. A terahertz spectrometer has been used within an Applied Materials<br>plasma reactor for process diagnostics. Studies have been completed which show that the<br>spectrometer can accurately measure densities of plasma constituents for a number gas<br>mixtures including $CF_2$ , FCN, HCN, CO and others. (1836.126, Frank C. DeLucia, Ohio S. U.)                                                                                                                                                               |

# **Energy Efficiency Thrust**

| Category                           | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy<br>Efficiency<br>(Circuits) | High-speed serial link receiver design and modeling techniques are proposed to significantly<br>improve interconnect bandwidth density in an energy-efficient manner. A statistical link<br>modeling tool was utilized to investigate the optimal equalization partitioning and modulation<br>format for 60+Gb/s signaling environments. A dual-mode NRZ/PAM4 SerDes was implemented<br>in GP 65-nm CMOS and achieved 16Gb/s NRZ and 32Gb/s PAM4 operation at 10.9 and<br>5.5mW/Gb/s, respectively. (1836.143, PI: S. Palermo, Texas A&M University)                                                                                                                                        |

| Energy<br>Efficiency<br>(Systems)  | Techniques to improve the rate, reliability, and energy efficiency of two-way between smart meters & data concentrators in smart grids using both narrow band power line communication (NB-PLC) and wireless communication are proposed. The narrowband (NB)-PLC/Wireless receiver diversity techniques improves the performance by exploiting the statistics of the impulsive noise in PLC. A new cyclostationary model for the NB-PLC noise based on frequency-shift (FRESH) filtering can be used to improve SNR by ~4dB. (1836.133, PIs: N. Al-Dhahir, UT-Dallas and B. L. Evans, UT-Austin)                                                                                            |

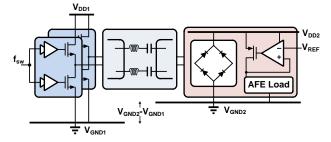

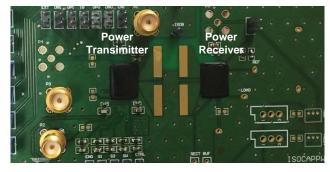

| Energy<br>Efficiency<br>(Circuits) | This project explores the circuit architecture and operation scheme for achieving highly power efficient on-silicon AC-DC power conversion in environmental sensor applications that is resilient to ground voltage disturbance. Capacitive isolation eliminates the bulky magnetics. However, the low density on-chip capacitor and large parasitics limit the output power level and efficiency. A resonant-based circuit architecture for power isolation with the peak power efficiency of 50.7% and the maximum output power of 62mW is demonstrated. This design achieves a 4X efficiency and a 3X power delivery improvement over the prior art. (1836.146, PI: Brian Ma, UT-Dallas) |

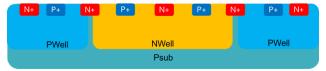

# TASK 1836.110, DISTRIBUTED POWER DELIVERY ARCHITECTURE FOR 2D AND 3D INTEGRATED CIRCUITS

SAIBAL MUKHOPADHYAY, GEORGIA INSTITUTE OF TECHNOLOGY, SAIBAL@ECE.GATECH.EDU

### SIGNIFICANCE AND OBJECTIVES

The primary objective is to design a low-loss, fully integrated, and robust distributed Power Delivery Unit for multicore processors targeting low output voltage from relatively high input voltage. The central innovation is a hybrid down conversion architecture composed of a central switched capacitor (SC) converter and multiple distributed inductive buck (IB) converter.

### **TECHNICAL APPROACH**

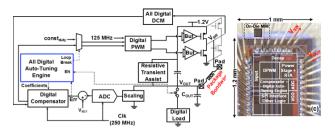

The key technical approach include design of the hybrid converter stage connecting switched capacitor back-end and inductive buck front-end. The key effort of last year focused on the optimizing the design of the buck stage. A single-inductor-multiple-output based buck stage was designed and integrated (off-chip) with the SC stage. We have also designed a two-phase buck stage. Finally, a very high-frequency buck stage was designed as well with fullydigital control and resistive assist based transient management circuits.

#### SUMMARY OF RESULTS

Design of a hybrid converter: A step down converter consisting of a switched capacitor stage followed by an inductive buck stage is designed. The SC converter is designed to produce a 4:1 down conversion from an unregulated 4.8V DC supply. The output of the switched capacitor is then fed to the feedback controlled inductive buck regulator. The buck regulator is designed in synchronous current mode control with load dependent variable frequency operation. The load current is sensed and after removal of high frequency components is fed to the oscillator that produces pulses proportional to the DC load current. The duty cycle can be adjusted to maximize the overall efficiency, by impedance matching among the load, buck converter and the switch capacitor converter. A test-chip is designed and taped-out in 130nm CMOS to study the characteristics of the hybrid converter. The testchip includes on-chip decoupling capacitors to minimize the effect of high-frequency noise due to bond-wires. The maximum conversion ratio designed to be 16.

**Single-Inductor-Multiple-Output (SIMO)**: We have presented a SIMO module that enables smaller passives for a given output power. First, Continuous Conduction Mode (CCM) operation is utilized to deliver higher output power for a smaller inductance; the cross-regulation in CCM operation is suppressed using a novel powerweighted CCM controller. Second, a modified power stage filter is presented using floating capacitors that utilizes Miller effect to reduce switching frequency of the output while maintaining power quality. The design is demonstrated through a 130nm CMOS test-chip that generates 4 outputs. The measurements demonstrate a 20MHz operation of the power stage with 500nH inductor and 1 $\mu$ F total load capacitance. DVS speed of 120mV/ $\mu$ s, and 73% peak efficiency at a load of 40mA are measured.

**High-frequency Buck Regulator**: We have designed a bond-wire inductance and on-die capacitance based high-frequency Integrated Voltage Regulator (IVR) with multi-sampled digital controller. We have also presented a resistive transient assist (RTA) circuit that utilizes multisampling and bypasses the control loop to provide charges to the output directly from input, thereby improving load and reference transients. An all-digital DCM mode and FET segment control are also included to improve low load efficiency. A 130nm CMOS test-chip demonstrates a 125MHz IVR with 250MHz compensator. The RTA circuit shows up to 2.5 x enhancements in transient settling times.

**Keywords:** Integrated converters, hybrid conversion, efficiency, high conversion ratio, packaging

#### INDUSTRY INTERACTIONS

Intel, IBM, Texas Instruments.

#### MAJOR PAPERS/PATENTS

[1] S. Carlo, et. al., "A High Power Density, Dynamic Voltage Scaling Compatible, Single-Inductor Four-Output Regulator using a Power-Weighted CCM Controller and a Floating Capacitor-Based Output Filter," IEEE TPE, Vol.31, No.6, June 2016, pp. 4252-4264.

[2] M. Kar, et. al, "A Scalable Hybrid Regulator for Down Conversion of High Input Voltage Using Low Voltage Devices," IEEE TPE, March 2016.

[3] M. Kar, et. al. "An Integrated Inductive VR with a 250MHz All-Digital Multisampled Compensator and on-Chip Auto-Tuning of Coefficients in 130nm CMOS." ESSCIRC, 2016.

[4] M. Kar, et. al, "Impact of the Process Variation in Inductive Integrated Voltage Regulator on Delay and Power of Digital Circuits," ISLPED, 2014.

[5] S. Carlo, et. al., "On the Potential of 3D Integration of Inductive DC-DC Converter for High-Performance Power Delivery," DAC, June 2013.

# TASK 1836.112, SHORTSTOP: FAST POWER SUPPLY BOOSTING FOR ENERGY-EFFICIENT, HIGH-PERFORMANCE PROCESSORS DAVID BLAAUW, UNIVERSITY OF MICHIGAN, BLAAUW@UMICH.EDU DENNIS SYLVESTER, UNIVERSITY OF MICHIGAN

#### SIGNIFICANCE AND OBJECTIVES

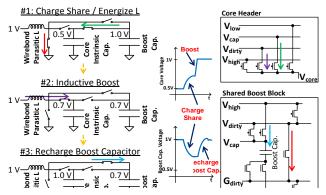

A novel core supply boosting technique, called Shortstop, is proposed as an alternative to on-chip regulators, which require expensive inductors. Instead Shortstop leverages the innate parasitic inductance of a dedicated dirty supply rail in a boost converter-type arrangement, along with an on-chip boost capacitor.

### **TECHNICAL APPROACH**

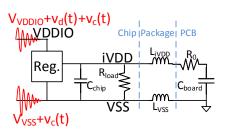

Figure 1 shows the high-level steps of Shortstop. On the first step Shortstop energizes the parasitic inductance of a wirebond pad by shorting it to ground. Simultaneously, an initial pre-boost of charge is delivered to the core through an on-chip boost capacitor. During step 2, the energized inductor is connected to the core (modeled as a decoupling capacitor), quickly raising the core's supply rail towards the target high voltage. Finally, once the core has reached its target high voltage any remaining charge in the parasitic inductance is used to charge the on-chip boost capacitor.

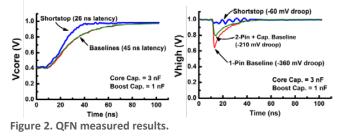

#### SUMMARY OF RESULTS

Figure 2 shows silicon measurements comparing boosting latency, as measured from when a boost is requested by the assertion of a 'go' signal to completing the boost, for the included M3 core using a baseline PMOS header based approach and Shortstop. The 1-pin baseline assumes Shortstop's hardware overhead can be amortized across multiple cores and hence is negligible, while the 2-pin baseline is a conservative estimate where the number of dirty supply pins equals the number of high supply pins. Vcore is the on-chip core supply net, as seen by the core

Figure 1. Overview of Shortstop concept.

being boosted. Vhigh is the clean "high voltage mode" supply net that could be shared among additional cores.

Modern processors, both high-performance and mobile, are packaged using flip-chip and not wirebonded. Instead of thin wires with relatively high inductance, flip-chip packaging uses bumps to connect high-density power and I/O signals to a substrate or circuit board. Because Shortstop leverages the parasitic inductance of a package, demonstration in flip-chip, with its lower parasitic inductance, is necessary. We propose an evolution of the first Shortstop prototype that includes flip-chip power delivery, improved boost topology, and an automated tuning algorithm to calibrate delay generators used with the boosting technique. Measured results in 40nm are given in [1].

Shortstop is demonstrated in 28nm wirebond and 40nm flip-chip implementations. In 28nm it boosts a 3nF core from 0.4V to 1.0V in 26ns while maintaining acceptable supply voltage droop. This boost latency is 1.8× faster than a header-based approach, while reducing supply droop by 2-7×, and can be used in near-threshold computing to overcome serial code bottlenecks. The 40nm version is capable of boosting Shortstop boosts a 2.7mm<sup>2</sup> core from 0.5V to 0.75V in 14ns with 27mV of droop on a shared 0.8V supply rail, marking a 57% faster transition with 67% lower supply noise than a dual-supply PMOS header design.

Keywords: DVFS, low power, CMOS, digital, microprocessor

#### INDUSTRY INTERACTIONS

IBM, Intel, Texas Instruments

#### MAJOR PAPERS/PATENTS

[1] N. Pinckney, D. Sylvester, and D. Blaauw, "Supply boosting for high-performance processors in flip-chip packages," *IEEE Europ. Solid-State Circuits Conf*, 2016.

[2] N. Pinckney, M. Fojtik, B. Giridhar, D. Sylvester, and D. Blaauw, "Shortstop: An on-chip fast supply boosting technique," *IEEE Symp. VLSI Circuits*, 2013.

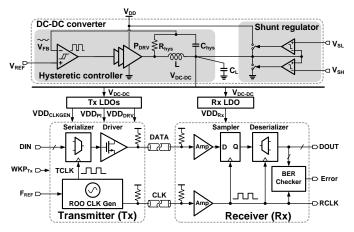

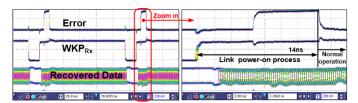

# TASK 1836.124, DIGITALLY-ENHANCED CLOCKING STRATEGIES TO IMPROVE ENERGY-EFFICIENCY OF SERIAL LINKS PAVAN KUMAR HANUMOLU, UNIVERSITY OF ILLINOIS, HANUMOLU@ILLINOIS.EDU

#### SIGNIFICANCE AND OBJECTIVES

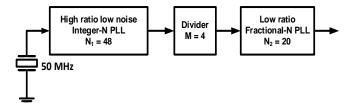

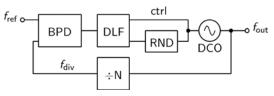

Proposed research presents the first fractional-N injection-locked clock multiplier that achieves the lowest power and jitter and hence the best figure-of-merit among all the reported fractional-N synthesizers.

### **TECHNICAL APPROACH**

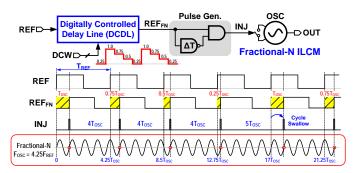

The idea behind the proposed fractional-N ILCM can be understood by considering the case of multiplication factor of 4.25 (N=4,  $\alpha$ =0.25) and the oscillator is initially set to oscillate at 4.25F<sub>REF</sub>. Noting that the oscillator accumulates an additional phase of 0.25T<sub>OSC</sub> every reference cycle, phase error between reference clock and oscillator output can be made zero by adding the same amount of phase shift to the reference clock as well. To this end, as depicted in Fig. 1, a digitally controlled delay line (DCDL) controlled by DCW is introduced. Gain of the DCDL must be calibrated as described in [1].

#### SUMMARY OF RESULTS

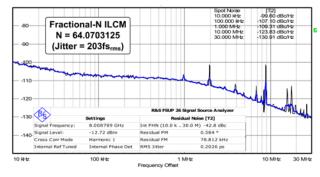

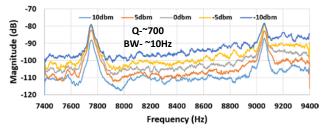

A prototype fractional-N ILCM is implemented in a 65nm CMOS technology and occupies an active area of 0.27mm<sup>2</sup>. At 8GHz, it consumes 3.25mW in fractional-N mode and 2.65mW in integer-N mode from a 0.9V supply, of which the DCO and its buffer consume less than 2.2mW. The performance of the ILCM is characterized using an external 125MHz reference clock that has about 190fsrms integrated jitter from 10kHz to 30MHz. Figure 4 shows the measured phase noise plots at 8GHz output frequency. In integer-N mode, integrated jitter is about 104fs<sub>rms</sub>. In fractional-N mode, the in-band phase noise is better than -107dBc/Hz at 100kHz offset frequency (Fig. 2). The integrated jitter is about 203fs<sub>rms</sub> and 240fs<sub>rms</sub> when the fractional spur is out-of-band and in-band, respectively. The proposed ILCM achieves the best power efficiency of 0.44mW/GHz and the first reported fractional-N clock multiplier with rapid on/off capability. It also achieves the best-reported FoM of -255dB (integer-N) and -247dB (fractional-N).

Figure 1. Block diagram of fractional-N injection locked clock multiplier.

Figure 2. Measured phase noise plot.

#### Keywords: fractional-N frequency synthesis, low power

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel

#### MAJOR PAPERS/PATENTS

[1] A. Elkholy, A. Elmallah, M. Elzeftawi, K. Chang, and P. Hanumolu, "A 6.75-to-8.25 GHz, 250fs<sub>rms</sub> integrated-jitter 3.25 mW rapid on/off PVT-insensitive fractional-N injection-locked clock multiplier in 65nm CMOS," in IEEE ISSCC Dig. Tech. Papers, Feb. 2016, pp. 192-193.

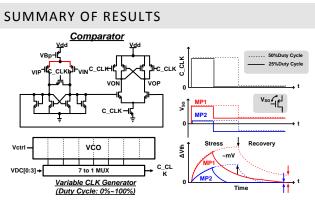

# TASK 1836.130, BUILT-IN SELF-TEST TECHNIQUES FOR TEST, CALIBRATION, AND TRIMMING OF POWER MANAGEMENT UNITS: PMU-BIST

SULE OZEV, ARIZONA STATE UNIVERSITY, SULE.OZEV@ASU.EDU

#### SIGNIFICANCE AND OBJECTIVES

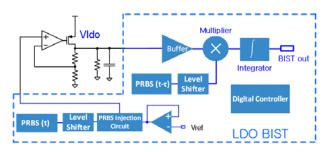

This project aims at (a) enabling trimming and calibration of PMU/PMICs through static measurements using small footprint BIST circuitry, (b) enabling dynamic testing through open-loop measurements and mathematical modeling, (c) fault analysis and grading approaches to identify design and layout issues, and (d) correlating trim coefficients with measurements.

#### **TECHNICAL APPROACH**

We have divided this problem into two parallel threads. First, our goal was to implement a very small foot-print, low frequency analog to digital converter that works in a particular voltage range (1-1.4V) and provides 10 bits of resolution (INL<1mV). Another goal was to implement a dynamic built-in-self-test system for the converter loop to test phase margin in order to evaluate loop stability.

#### SUMMARY OF RESULTS

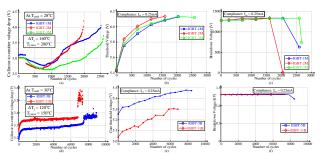

The zoom-in ADC was designed and taped out at TI India in 2016. Figure 1 shows the results from the zoom-in ADC. The INL of the ADC is below the target 1mV for window sizes below 100mV. This would indicate a 2-step conversion for the ADC. The overall measurement time is 100ms per DC measurement.

The dynamic BIST system is shown in Figure 2. All of the system components are implemented in 40-nm GF technology and taped out at NXP, Austin, TX. The overall area of the BIST circuit is 0.019mm<sup>2</sup> and the evaluation time is 20ms. Figure 3 shows the comparison of the BIST

|             | INL(mV)     |             |  |  |  |  |

|-------------|-------------|-------------|--|--|--|--|

| 100mV       | 200mV       | 300mV       |  |  |  |  |

| 0.052728774 | 0.101196247 | 0.151964231 |  |  |  |  |

| 0.051742842 | 0.100101595 | 0.151045837 |  |  |  |  |

| 0.094101648 | 0.178332401 | 0.253850356 |  |  |  |  |

| 0.094286797 | 0.178578628 | 0.254121085 |  |  |  |  |

Figure 1. INL of the zoom-in VCO for 100mV, 200mV, and 400mV zoom window at two different temperatures (25°C shown in pink and 85°C shown in orange). Measurements are taken at Texas Instruments, India.

Figure 2. Dynamic BIST for LDO's.

| lload<br>(mA) | BIST                              | Loop<br>Analysis                  |

|---------------|-----------------------------------|-----------------------------------|

| 20            | <b>60</b> <sup>0</sup>            | 59 <sup>0</sup>                   |

| 30            | <b>51</b> <sup>0</sup>            | <b>50</b> . <b>5</b> <sup>0</sup> |

| 40            | <b>44</b> <sup>0</sup>            | 45 <sup>0</sup>                   |

| 50            | <b>40</b> . <b>2</b> <sup>0</sup> | <b>40</b> . 7 <sup>0</sup>        |

Figure 3. BIST results compared with loop analysis for phase margin.

circuit response at various load current values to a more traditional technique for phase margin evaluation.

## Keywords: BIST, PMU, phase margin, bandgap reference

#### INDUSTRY INTERACTIONS

Texas Instruments, NXP

#### MAJOR PAPERS/PATENTS

[1] Navankur Beohar, Priyanka Bakliwal, Sidhanto Roy, Debashis Mandal, Bertan Bakkaloglu, Sule Ozev, "Disturbance-free BIST for Loop Characterization of DC-DC Buck Converters", IEEE VLSI Test Symposium, 2015. (Received best paper honorable mention award)

[2] Osman Emir Erol, Sule Ozev, Chandra Suresh, Rubin Parekhji, and Lakshmanan Balasubramanian. "On-chip measurement of bandgap reference voltage using a small form factor VCO based zoom-in ADC." IEEE Design, Automation & Test in Europe Conference, pp. 1559-1562, 2015.

[3] Liu, Tao, Chao Fu, Sule Ozev, and Bertan Bakkaloglu. "A built-in self-test technique for load inductance and lossless current sensing of DC-DC converters." IEEE VLSI Test Symposium (VTS), 2014. (Received Best paper award)

TASK 1836.133, ENERGY-EFFICIENT SIGNAL PROCESSING TECHNIQUES FOR SMART GRID HETEROGENEOUS COMMUNICATION NETWORKS NAOFAL AL-DHAHIR, THE UNIVERSITY OF TEXAS AT DALLAS, ALDHAHIR@UTDALLAS.EDU BRIAN L. EVANS, UNIVERSITY OF TEXAS AT AUSTIN

#### SIGNIFICANCE AND OBJECTIVES

Smart Grids are supported by heterogeneous networks that employ both wireless and powerline communication (PLC) technologies since no single solution fits all scenarios. We propose a reliable hybrid power line and wireless communication transceiver for Smart Grids.

#### **TECHNICAL APPROACH**

We focus on the last mile communication link between the utility data concentrator and the residential smart meter. The transceiver is implemented over power lines in the narrowband 3-500 kHz frequency band and also over the unlicensed wireless frequency band from 902 MHz to 928 MHz. The interference on both the narrowband power line communication and the unlicensed wireless communication links is impulsive in nature. To mitigate such impulsive noise on both links, we propose a hybrid PLC/wireless communication transceiver where both links carry the same information data. We present efficient receiver diversity combining techniques for the PLC and wireless signals that takes into account the impulsive nature of the interference.

#### SUMMARY OF RESULTS

We propose PLC/Wireless receiver combining techniques based on maximal-ratio-combining (MRC) that take into account the impulsive nature of noise on the two links. In particular, for coherent modulation schemes, we PLC/Wireless present three receiver combining techniques with different performance/complexity tradeoffs. The proposed techniques are: average-SNR combining (ASC), power spectral density combining (PSC) and instantaneous-SNR combining (ISC). Furthermore, for differential modulation, we propose a diversity combining technique based on the received signal power and the noise PSD which outperforms the conventional average SNR and equal gain combining techniques over the whole operating SNR range.

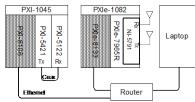

In addition, we implemented a flexible real-time testbed to evaluate the proposed diversity combining schemes over physical PLC and wireless channels. The testbed realizes essential parts of the physical layers on which both powerline and wireless communications operate.

The real-time testbed is built using products from National Instruments. The PLC and wireless communications will be located in different places as they need different physical channels. Therefore, the two communication systems reside in different chassis. A PXI chassis has slots that can accommodate an x86 controller and various modules. As Fig. 1 depicts, a PXI-1045 chassis on the left has a PXI-8106 controller, a PXI-5421 signal generator and a PXI-5122 digitizer. This chassis functions as a baseband PLC system. Similarly, a PXIe-1082 chassis contains a PXIe-8133 controller, a PXIe-7965R FPGA module and an NI-5791 RF adapter module. Since the RF adapter module has both a transmit and a receive port, a unidirectional single-input single-output link can be established with a single adapter module.

Figure 1. Hardware architecture.

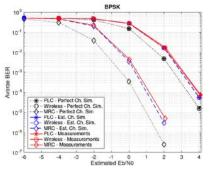

The performance of the proposed combining techniques measured on the testbed is compared with computer simulation results by plotting BER curves for binary phase-shift keying (BPSK) modulation in Fig. 2 for both perfect and estimated channel scenarios.

Figure 2. BER performance versus E<sub>b</sub>/N<sub>o.</sub>

**Keywords:** smart grids, power line and wireless communication, diversity, periodic impulsive noise

#### **INDUSTRY** interactions

Texas Instruments, NXP

#### MAJOR PAPERS

[1] M. Sayed, T. Tsiftsis, and N. Al-Dhahir, "On the Diversity of Hybrid Narrowband-PLC/Wireless Communications for Smart Grids", to appear in IEEE Transactions on Wireless Communications, 2017.

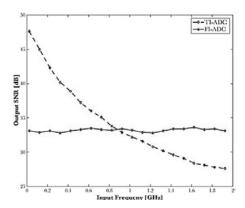

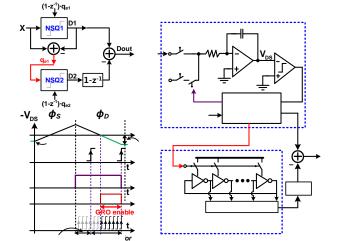

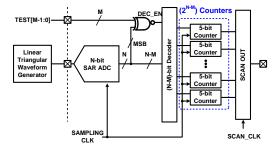

# TASK 1836.138, MICRO-POWER ANALOG-TO-DIGITAL DATA CONVERTERS

GABOR C. TEMES, OREGON STATE UNIVERSITY, TEMES@ENGR.ORST.EDU

#### SIGNIFICANCE AND OBJECTIVES

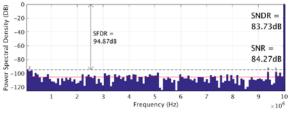

The objective of the project was to develop improved architectures and circuits, as well as improved design processes for micro-power incremental and extendedcounting analog-to-digital converters. The new concepts were then verified by the implementation and testing of appropriate test devices. The results far exceeded the state-of-the-art.

#### **TECHNICAL APPROACH**

Incremental analog-to-digital converters (IADCs) allow a single ADC to service multiple sensors. Our research developed novel IADC architectures that achieved both high accuracy and excellent power efficiency. We have found some particularly useful new IADC configurations, which need only a single active component used multiple times to achieve an excellent accuracy. This breakthrough hardware-recycling technique extends the accuracy of the converter with very low power consumption. Compared to the conventional single-step IADC of the same accuracy, the new ADCs reduce the power requirement by a factor of close to 1000. Fabricated on a chip, the novel device demonstrated superior performance.

#### SUMMARY OF RESULTS

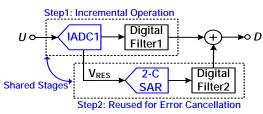

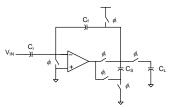

Our last device realized a two-step incremental ADC (IADC) using extended counting [1]. In the first step, the IADC is configured as a first-order  $\Delta\Sigma$  loop with an input feedforward architecture. In the second step, a two-capacitor SAR-assisted extended counting enhances the accuracy. A single active integrator is shared in both steps. The block diagram of the device is shown in Fig. 1.

Figure 1. Conceptual block diagram of the proposed two-step IADC.

The period between adjacent resets is divided into two intervals. During the first step, the IADC realizes a first-order  $\Delta\Sigma$  loop with a feedforward architecture. In the second step, when the control signal  $EN_{S2}$  goes high, the input path is disconnected. The quantization residue  $V_{RES}$  is quantized during the next M<sub>2</sub> periods by a SAR ADC,

implemented by a two-capacitor DAC and the same integrator as used in the first step.

The prototype test chip was fabricated in a 0.18- $\mu$ m CMOS process. Table I summarizes the measured performance of the prototype IADC, and compares it with state-of-art IADCs of earlier architectures. The IADC achieves a peak SNR/SNDR/DR of 97.1/96.6/100.2 dB over a 1.2 kHz bandwidth, while dissipating 33.2  $\mu$ W from a 1.5 V supply. This gives a Schreier FoM of 175.8 dB and Walden FoM of 0.25 pJ/conv.-step, both among the best values. The combination of hardware recycling and SAR-assisted extended counting technique results in the reduction of both the power dissipation and the chip core area.

| Parameter                                  | This<br>Work                  | JSSC15          | VLSI16                        | ISSCC16     | ISSCC13         |

|--------------------------------------------|-------------------------------|-----------------|-------------------------------|-------------|-----------------|

| Architecture                               | IADC1 +<br>Binary<br>Counting | IADC2<br>+IADC1 | IADC1<br>+<br>Multi-<br>Slope | Zoom<br>ADC | Single<br>IADC2 |

| Technology<br>(nm)                         | 180                           | 65              | 180                           | 160         | 160             |

| Area (mm <sup>2</sup> )                    | 0.27                          | 0.2             | 0.32                          | 0.16        | 0.45            |

| Sampling<br>Freq. (kHz)                    | 642                           | 192             | 642                           | 11000       | 750             |

| Bandwidth<br>(kHz)                         | 1.2                           | 0.25            | 1                             | 20          | 0.667           |

| Power (µW)                                 | 33.2                          | 10.7            | 34.6                          | 1650        | 20              |

| SNRmax<br>(dB)                             | 97.1                          | -               | 98.4                          | 104.4       | -               |

| SNDRmax<br>(dB)                            | 96.6                          | 90.8            | 96.8                          | 98.3        | 81.9            |

| DR (dB)                                    | 100.2                         | 99.8            | 99.7                          | 107.5       | 81.9            |

| $FoM_{S}^{1}(dB)$                          | 175.8                         | 173.5           | 174.6                         | 178.3       | 157.1           |

| FoM <sup>2</sup> <sub>W</sub><br>(pJ/conv) | 0.25                          | 0.76            | 0.32                          | 0.32        | 1.48            |

Table 1. Comparison with the state of the art.

**Keywords:** multi-step incremental ADC, SAR-assisted, delta-sigma, extended counting, two-capacitor SAR

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] Zhang, Y.,C-H Chen, He, T. and G.C. Temes, "A twocapacitor SAR-assisted multi-step incremental ADC with a single-amplifier achieving 96.6 dB SNDR over 1.2 kHz BW," IEEE Custom Integrated Circuits Conf., Austin, TX, Apr. 30 – May 3, 2017.

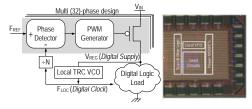

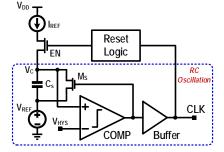

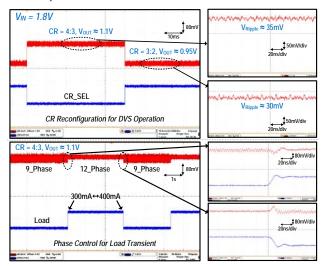

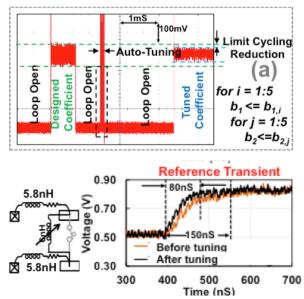

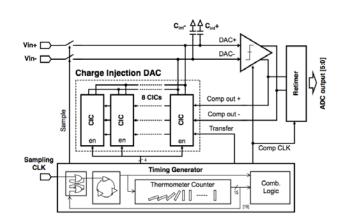

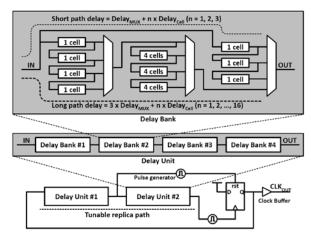

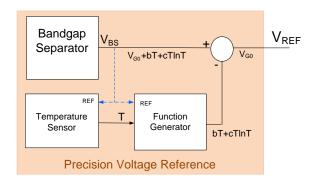

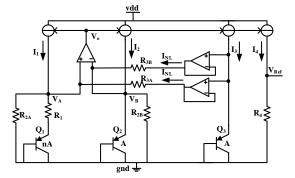

Voltage regulators in advanced SoC's are expected to achieve transient speed and power density higher than conventional regulators. In this project, three major issues in development of VHF (30-300 MHz range) multiphase switching regulators are investigated: high-speed feedback control, clock synchronization, and system miniaturization.

### **TECHNICAL APPROACH**

From the perspective of control scheme, compared to its voltage-mode counterparts, the proposed currentmode approach is more robust to the noise at output voltage, as the sensed control vector is inductor current. From the perspective of system operation and circuit topology, interleaved multiphase topology can effectively improve the system response. By taking advantage of the proposed current-mode hysteretic control, a simple clock synchronization technique is proposed which achieves cycle-by-cycle regulation in each sub-converter.

From the perspective of system implementation, monolithic implementation of the regulator, which allows the power flow to follow the desired paths to reduce the parasitic is being investigated.

#### SUMMARY OF RESULTS

The challenge in the modern design of switching power converters has been to develop a fully integrated switching converter, which meets the additional demand for system miniaturization. In order to develop a fully integrated switching converter, it becomes necessary to operate in VHF regime to reduce the inductive and capacitive components in the power stage and to eliminate other bulky off-chip components.

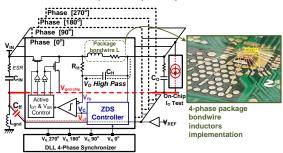

Figure 1. Block diagram of the four-phase buck converter with the photo of the package bondwire inductors implementation.

In this project, a fully on-chip integrated multiphase converter is proposed, and the system block diagram is shown in Figure 1. The four sub-converters are phasesynchronized by a built-in DLL-based synchronizer. As the proposed dual-loop control is independently conducted in each sub-converter, cycle-by-cycle current balancing is inherently implemented between phases. Moreover, the benefit of a multiphase operation is that it can achieve reduced passive components size and ns-level transient response. Thus, the required inductor size is significantly reduced to the range of the package bond wires, enabling implementation of the power inductor by using package bond wires as shown in Fig. 1. Accordingly, the system form factor, transient response, and power density have been significantly improved.

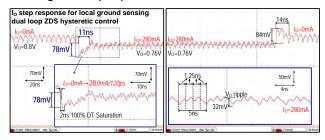

Figure 2. Measured load transient response to a load step from 0 to 280mA within 120ps with on-chip 1.97nF capacitor.

Fig. 2 shows the measured transient response and the output voltage ripple. The proposed converter employs a 1.8nF input capacitor, a 1.97nF output capacitor, and four 6.5nH bond-wire inductors without any other external components. In response to a 280mA/120ps load step-up, the voltage droop is 78mV (9.8% of output voltage) with 11ns response time. For load step-down, the converter exhibits 84mV overshoot within 14ns of 1% settling time. The output voltage ripple is maintained at 32 mV.

**Keywords**: fully integrated converters, VHF switching converters, multi-phase operation, feedback control

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] M. Song, et al., "A 200-MHz 4-Phase Voltage Regulator with Local Ground Sensing Dual Loop ZDS Hysteretic Control Using 6.5nH Package Bondwire Inductors on 65nm Bulk CMOS," (Invited) in 2016 ASP-DAC, pp. 1422-1425, Jan. 2014.

# TASK 1836.140, EMBEDDED & ADAPTIVE VOLTAGE REGULATORS WITH PROACTIVE NOISE REDUCTION FOR DIGITAL LOADS UNDER WIDE DYNAMIC RANGE

ARIJIT RAYCHOWDHURY, GEORGIA TECH, ARIJIT.RAYCHOWDHURY@ECE.GATECH.EDU

#### SIGNIFICANCE AND OBJECTIVES

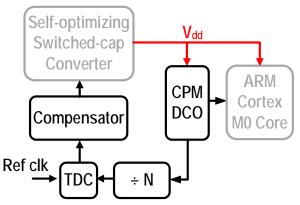

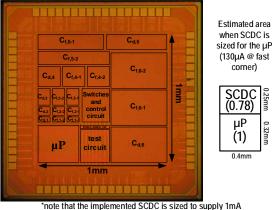

The primary goal of the project is to develop an integrated power flow architecture for fine-grained spatio-temporal voltage distribution and management in microprocessors and SoC's. We investigate through models, simulations, hardware development and experimentation novel control topologies and circuit techniques for efficient wide-dynamic range linear and switched capacitor VR's.

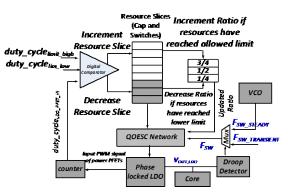

#### TECHNICAL APPROACH

This project investigates power flow architecture in microprocessors and SoCs. There are two primary thrusts here: (1) development of novel control topologies for all digital linear regulators for Point of Load (PoL) regulation and (2) use of switched capacitor on-die regulators to provide power on demand for distributed IP blocks. In this phase of the program, the major accomplishments have been on the development of novel PoL topologies, circuit prototyping and measurements.

#### SUMMARY OF RESULTS

In the past year of performance, we have continued to investigate (1) switched mode control for ultra-fast droop recovery (2) a novel unified voltage and frequency (UVFR) topology that allows operation of digital load circuits under fine-grained DVFS states while continuing to work during a voltage droop or during PLL relocking, and (3) a multiple output switched capacitor VR. In switched mode control, the LDO differentiates between small signal regulation and the large signal performance. Small signal regulation is handled by an output pole dominant analog loop, whereas the large signal transients are handled by a

Figure 1. Switched Mode Control for LDO.

Figure 2. Unified Voltage and Frequency Regulation.

Figure 3. Multi-output SCVR architecture.

digital loop (Fig. 1). Measurements show peak response time of 18 ns for large load transients, low voltage operation programmability and a peak current efficiency of 98.64%. Motivated by the observation that the main objective of supply voltage regulation in digital systems is meeting timing, we present a Unified Voltage Frequency Regulator (UVFR) that sets the supply voltage based on system timing properties, and minimizes supply noise margins by temporarily modulating the clock frequency. Measured data on a 130nm test-chip across a wide range of voltage and current inputs reveals peak current efficiency of 99.4% and 27% supply reduction at isoperformance through adaptation and resiliency which are intrinsic to the control loop. We have also proposed a multiple output SCVR (Fig. 3). This allows co-regulation across four different voltage domains and peak measured efficiency of 84%.

**Keywords:** integrated voltage regulator, discrete control, continuous time control, LDO, switched mode control

#### INDUSTRY INTERACTIONS

Intel, IBM

#### MAJOR PAPERS/PATENTS

[1] S. Gangopadhyay et al., CICC, 2017.

[2] Saad Nasir, et al. Applied Power Electronics Conference and Exposition (APEC), 2015.

- [3] Saad Nasir, et al. ISSCC, 2015.

- [4] Saad Nasir et al., Transactions on Power Electronics.

- [5] S. Gangopadhyay et al., JSSC, 2014.

- [6] Saad B. Nasir, et al. ISCAS, 2016.

- [7] Saad B. Nasir, et al. ESSCIRC, 2016.

- [8] S. Gangopadhyay et al., ESSCIRC, 2016.

- [9] S. Gangopadhyay et al., DAC, 2015.

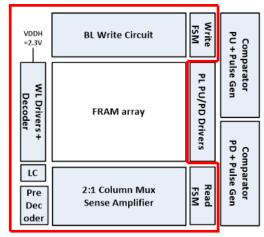

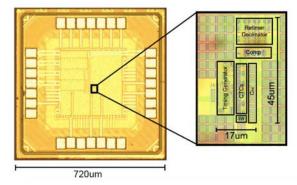

The focus of our research is on ultra-low energy FRAM arrays for millimeter-scale sensors. The objective is to optimize FRAM for ultra-low energy operation by using an adiabatic design to reduce write energy, especially for large block writes. This report details the current test results on the FRAM prototype chip.

#### **TECHNICAL APPROACH**

The approach uses resonance to reduce energy consumption. To start the resonance PL is stepped to  $V_{DD}/2$ . To write new data into a row, the BLs are switched to data adiabatically by controlling the WREN and PLEN, i.e. the starting point and ending point for data '0' is 0 of PL and for data '1' is  $V_{DD}$  of PL. Each row needs one and a half cycle of resonance to write a new data, with its word-line asserted. The WL signals are overdriven to  $(V_{DD}+V_{TH})$  to compensate for the  $V_{TH}$  drop across NMOS access transistor.

#### SUMMARY OF RESULTS

Fig. 1 shows the die picture of the FRAM prototype chip in a 130nm process node. It has an array size of 512x80 in 1T-1C mode, and 256x80 in the 2T-2C mode.

The prototype chip for the adiabatic FRAM design has been fabricated, and we received the dies earlier this year. The chip was then packaged, and in parallel a test board was designed, which has the LC tank on the board.

Currently, the chip is being tested. Read and write operations on the FRAM have been validated on this prototype with a conventional square waveform. The nonvolatile behavior has also been tested by writing and reading across a power off sequence.

Figure 1. Die photo – 130 nm FRAM prototype chip.

Fig. 2 shows the block diagram of the FRAM prototype chip. The validation of read and write with a square

waveform has allowed us to test the peripherals inside the red boundary.

Figure 2. FRAM prototype block diagram.

For the circuit to resonate, the LC tank on the board has to be tuned with the board parasitic, and the pad parasitic, in addition to the FRAM block inside the chip. Once we find the correct LC values, it will also allow us to characterize the adiabatic FRAM, and validate the adiabatic operation. Currently, we are debugging the resonance circuits, and will share the testing results for the sinusoidal waveform based adiabatic operation, once available.

**Keywords:** low power, memory, non-volatile, CMOS, electronics

INDUSTRY INTERACTIONS

Texas Instruments, NXP MAJOR PAPERS/PATENTS

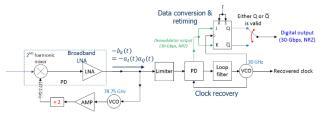

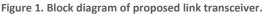

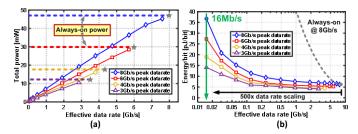

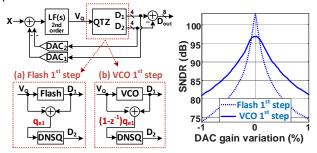

# TASK 1836.143, DESIGN TECHNIQUES FOR MODULATION-AGILE AND ENERGY-EFFICIENT 60+GB/S RECEIVER FRONT-ENDS SAMUEL PALERMO, TEXAS A&M UNIVERSITY, SPALERMO@ECE.TAMU.EDU

#### SIGNIFICANCE AND OBJECTIVES

While high-performance I/O circuitry can leverage CMOS technology improvements, unfortunately the bandwidth of the electrical communication channels has not scaled in the same manner. The high-speed serial link receiver design and modeling techniques proposed here aim to significantly improve interconnect bandwidth density in an energy-efficient manner.

#### **TECHNICAL APPROACH**

In order to investigate design trade-offs, a statisticalmodeling framework will be utilized to investigate poweroptimum equalization partitioning and modulation format for 60+Gb/s signaling environments. This tool will be used to guide the design of a new modulation-agile receiver front-end which includes a multi-level decision-feedback equalizer (DFE) with multiple FIR/IIR feedback taps for efficient long-tail ISI cancellation. Adaptive techniques will also be developed to tune key equalization parameters, such as DFE tap time constants/weights and CTLE settings.

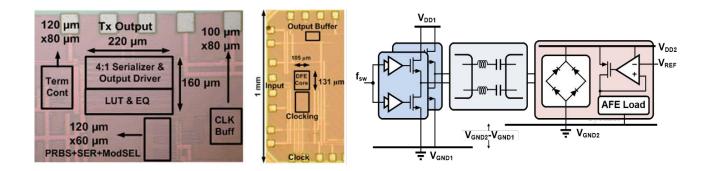

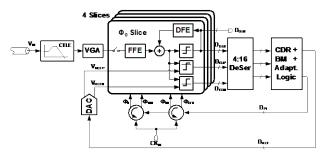

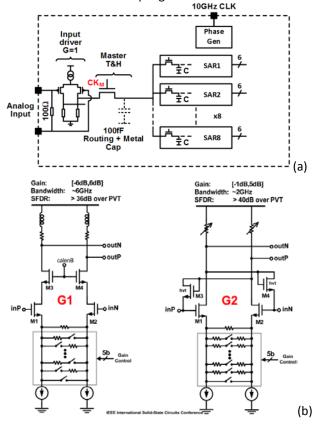

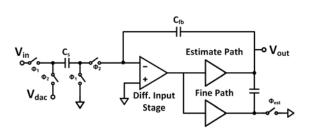

#### SUMMARY OF RESULTS

PAM4 modulation offers the potential to support everincreasing serial I/O bandwidth density demands. While dedicated PAM4 transceivers have been developed, the majority of serial I/O standards use simple binary NRZ modulation. In order to address this, a dual-mode

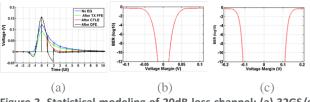

Figure 1. 16/32Gb/s dual-mode NRZ/PAM4 SerDes in GP CMOS: (a) transmitter, (b) receiver, and (c) performance summary.

Figure 2. Statistical modeling of 20dB loss channel: (a) 32GS/s pulse response with and without equalization, (b) 64Gb/s PAM4 bathtub curve, and (c) 32GB/s NRZ bathtub curve.

NRZ/PAM4 SerDes which seamlessly supports both modulations with a 1-FIR- and 2-IIR-tap DFE receiver and a 4/2-tap FFE transmitter in NRZ/PAM4 modes, respectively, was developed [1, 2]. A source-seriesterminated (SST) transmitter employs lookup-table (LUT) control of a 31-segment output DAC to implement FFE equalization in NRZ and PAM4 modes with a  $1.2-V_{pp}$ output swing and utilizes low-overhead analog impedance control. Optimization of the guarter-rate transmitter serializer is achieved with a tri-state inverter-based mux with dynamic pre-driver gates. The quarter-rate DFE receiver achieves efficient equalization with 1-FIR tap for the large first post-cursor ISI and 2-IIR taps for long-tail ISI cancellation. Fabricated in GP 65-nm CMOS (Figure 1), the transceiver occupies 0.074 mm<sup>2</sup> area and achieves power efficiencies of 10.9 and 5.5 mW/Gbps with 16Gb/s NRZ and 32Gb/s PAM4 data, respectively.

At low BER's, transient simulations are impractical. To investigate this, this project continues to build upon the PI's statistical-modeling framework for high-speed serial links. While receiver-side DFE equalization is very power efficient for cancelling post cursor ISI, its effectiveness is limited by large pre-cursor ISI in channels with more than 15dB of loss in PAM4 mode (Figure 2). Link simulations indicate that an efficient way to deal with pre-cursor ISI is to use a pre-cursor FFE equalizer tap at the transmitter side and RX CTLE. This provides sufficient voltage margin for both 64Gb/s PAM4 and 32Gb/s NRZ operation.

**Keywords:** decision feedback equalizer, infinite impulse response (IIR) DFE, receiver, serial link

#### INDUSTRY INTERACTIONS

IBM, Texas Instruments

#### MAJOR PAPERS/PATENTS

[1] A. Roshan-Zamir et al., "A 16/32 Gb/s Dual-Mode NRZ/PAM4 SerDes in 65nm CMOS," IEEE CSICS, 2016.

[2] A. Roshan-Zamir et al., "A Low-Overhead Reconfigurable 16/32 Gb/s Dual-Mode NRZ/PAM4 SerDes in 65nm CMOS," accepted in IEEE JSSC.

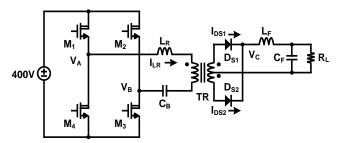

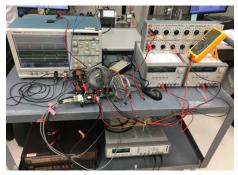

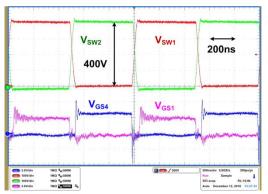

This research aims to investigate novel soft-switching techniques, synchronous gate driving techniques, and control schemes to significantly advance power efficiency and power density of today's high-voltage DC-DC converters. These developed converter technologies help greatly lower the cost and improve the energy efficiency of renewable energy, telecom, automotive and other systems.

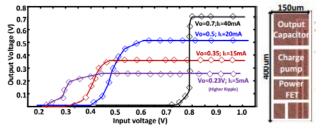

#### **TECHNICAL APPROACH**