# TEXAS ANALOG CENTER OF EXCELLENCE

ERIK JONSSON SCHOOL OF ENGINEERING AND COMPUTER SCIENCE

# Annual Report 2020 – 2021

# **TXACE MISSION**

The Texas Analog Center of Excellence seeks to create fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

# **TXACE THRUSTS**

Safety, Security and Health Care

Energy Efficiency

Fundamental Analog Circuits

# TxACE 2020–2021 ANNUAL REPORT

The Texas Analog Center of Excellence (TxACE), located at the University of Texas at Dallas is the largest analog research center based in an academic institution. Analog and mixed signal integrated circuits engineering is both a major opportunity and challenge. Analog circuitry is a critical component of the majority of products for the \$400+ billion per year integrated circuits industry, as a part of sensing, actuation, communication, power management and others. Digital integrated circuits such as microprocessors, logic circuits and memories are now integrating analog functions such as input/output circuits, phase locked loops, temperature sensors and power management circuits. It is also common to find microcontrollers with multiple analog-to-digital and digital-to-analog converters. These circuitries impact almost all aspect of modern life: safety security, health care, transportation, energy, entertainment and others.

Creation of advanced analog and mixed signal circuits and systems depends on the availability of engineering talent for analog research and development. TxACE was established to help translate the opportunity into economic benefits by overcoming the challenge and meeting the need. TxACE was established through a collaboration of the state of Texas, Texas Instruments, the Semiconductor Research Corporation, the University of Texas System, and The University of Texas at Dallas.

The research tasks are organized into three research thrust areas: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog. The scope of investigation extends from circuits operating at dc through terahertz, data converters that sample at a few samples/sec to 10's of Giga-samples/sec, AC-to-DC and DC-to-AC converters working at  $\mu$ W to Watts, energy harvesting circuits, sensors and many more. Significant improvements to existing mixed signal systems and new applications have been made and continued to be anticipated. Students who have been exposed to hands-on innovative research are forming the leading edge of analog talent flow into the industry. Close collaboration with and responsiveness to industry needs provide focus to the educational experience.

#### DIRECTOR'S MESSAGE

The Texas Analog Center of Excellence (TxACE) is leading analog research and education. During this second year of COVID-19 pandemic, the Center has focused on executing its core mission, in turn is creating technologies that are helping our world better manage through this challenging time. We are privileged to be able to contribute toward this.

The Center funded 89 research tasks led by 74 principal investigators at 33 institutions, including three international universities. The Center supported 201 graduate and undergraduate students.

Over the past year, TxACE researchers published 30 journal and 41 conference papers. We also filed 5 patent applications and 4 invention disclosures and were granted 4 patents. 23 Ph.D. and 3 M.S. students have completed their degree program.

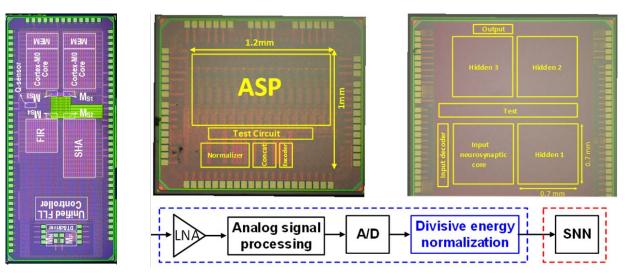

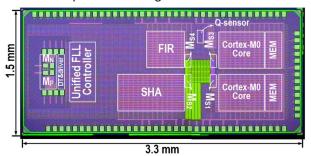

There are always too many research accomplishments to list all here. A selected list includes demonstration of an end-to-end

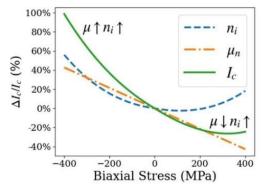

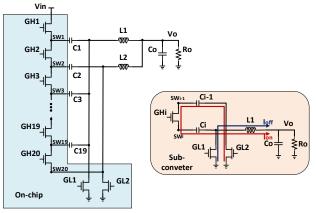

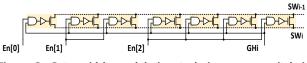

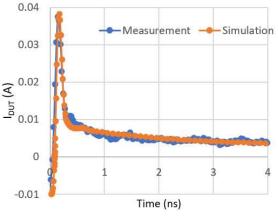

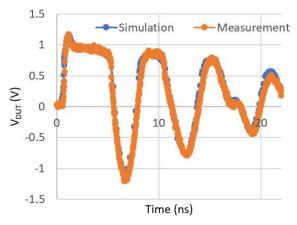

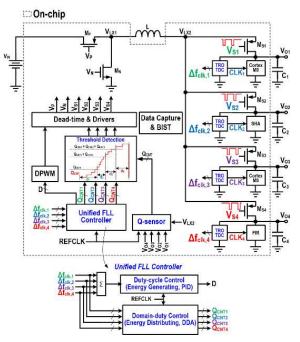

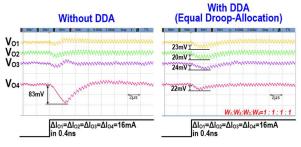

key word spotting system that consumes 205~570nW power and scales with input rate due to use of a fully spike-event-driven classifier, discovery that the compressive biaxial stress common in most commercial packages increases intrinsic carrier concentration and electron mobility in npn transistors, both of which increase collector current, demonstration of an RC 100-MHz frequency reference fabricated in 65-nm CMOS achieving an inaccuracy of ±140ppm over -40 to 95°C and 1µW/MHz power efficiency, and a domain-scalable run-time programmable integrated voltage regulator fabric using a single inductor multiple output (SIMO) buck converter for power-delivery and regulation.

The TxACE laboratory is continuing to help advance integrated circuit research by making its instruments and expertise available to researchers and our industrial partners all over the world.

I am happy to report that MediaTek has joined TxACE and SRC. I would like to thank UT Dallas, the University of Texas System, TI, and SRC, as well as many friends of TxACE all over the world for their generous support. Lastly, I would like to thank the students, principal investigators and staff for their efforts. I look forward to another year of working with the TxACE team to make our way of life better, safer and healthier through our research, education and innovation.

Most importantly, I wish everybody health and safety.

Kenneth K. O, Director TxACE Texas Instruments Distinguished University Chair Professor The University of Texas at Dallas

#### **BACKGROUND & VISION**

The \$450+ billion per year integrated circuits industry is evolving into an analog/digital mixed signal industry. Analog circuits are providing or supporting critical functions such as sensing, actuation, communication, power management and others. These circuits impact almost all aspect of modern life including safety, security, health care, transportation, energy, and entertainment. To lead this change, in particular to lead analog and mixed signal technology education, research, commercialization, manufacturing, and job creation, the Texas Analog Center of Excellence was announced by Texas Governor Rick Perry in October 2008 as a collaboration of the Semiconductor Research Corporation, state of Texas through its Texas Emerging Technology Fund, Texas Instruments Inc., University of Texas system and University of Texas at Dallas. The Center seeks to accomplish the objectives by creating fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, healthcare, and public safety and security as well as by improving the research and educational infrastructure.

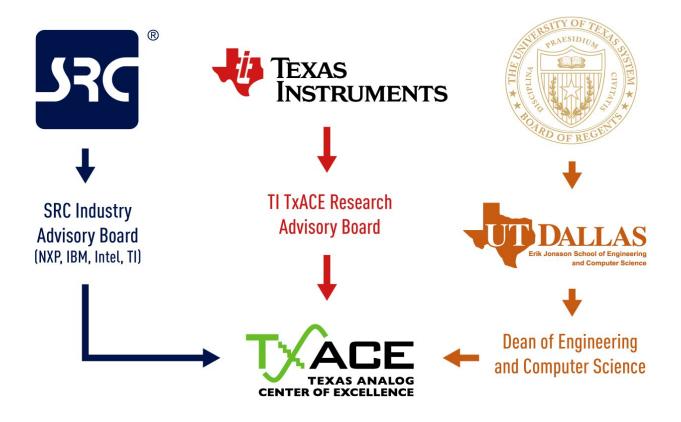

Figure 1. TxACE organization relative to the sponsoring collaboration (2019-2020).

#### **CENTER ORGANIZATION**

The Texas Analog Center of Excellence is guided by agreements established with the Center sponsors. Members of the industrial advisory boards identify the research needs and select research tasks in consultation with the Center leadership. Figure 1 diagrams the relationship of TxACE to the members of the sponsoring collaboration.

# The internal organization of the Center is structured to flexibly perform the research mission while fully embracing the educational missions of the Universities.

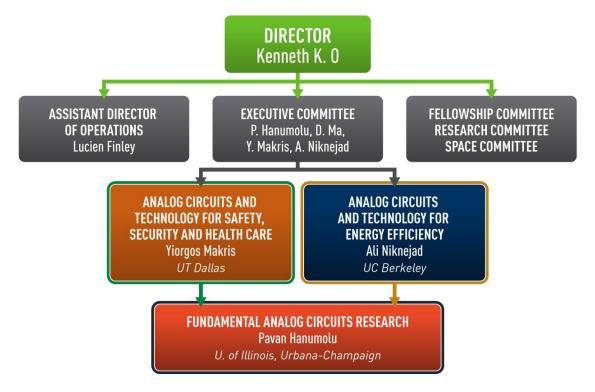

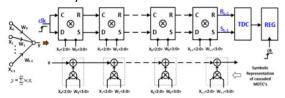

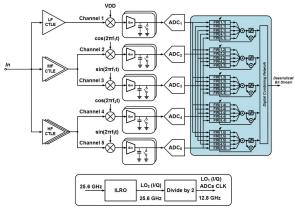

Figure 2 shows the center management structure. The TxACE Director is Professor Kenneth O. The research is arranged into three thrusts that comply with the center mission: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog Research. The third thrust consists of vital research that cuts across the first two research thrusts. The thrust leaders are Prof. Yiorgos Makris of the University of Texas at Dallas for safety, security and health care, and Prof. Ali Niknejad of the University of California, Berkeley for energy efficiency. The leader for fundamental analog is Prof. Pavan Hanumolu of University of Illinois, Urbana-Champaign. The thrust leaders along with Professor Dongsheng Ma of the The University of Texas at Dallas for productivity by increasing collaboration, better leveraging the diverse capabilities of principle investigators of the Center, and lowering research barriers. The leadership team also identifies new research opportunities for consideration by the Industrial Advisory Boards.

Figure 2. TxACE organization for management of research

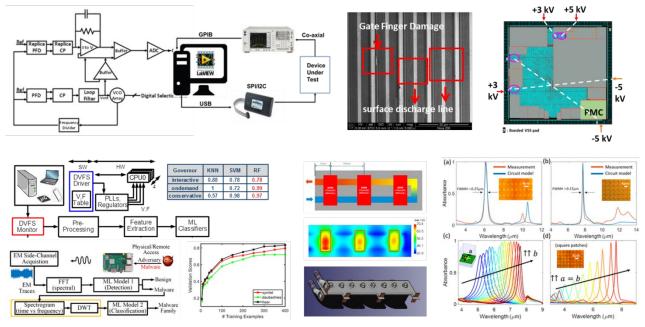

#### SAFETY, SECURITY & HEALTH CARE

(Thrust leader: Yiorgos Makris, University of Texas at Dallas)

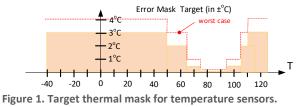

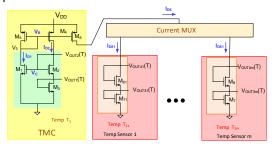

The portfolio of TxACE research activities includes a broad range of analog technologies which seek to promote public safety and security, as well as to improve health care. Efforts in this thrust focus on improving safety by mitigating various reliability threats in analog/RF devices, including ESD, supply noise, temperature stress/strain and electro-migration, as well as by developing effective machine learning-based design, verification and self-test solutions. Particular emphasis has been placed on characterizing circuit aging, predicting failures and increasing lifetime of nano-scale CMOS circuits. This thrust also seeks to reduce the cost of millimeter wave imaging and on-vehicle radar technology for automotive safety by researching signal processing techniques that reduce system complexity and transmitter architecture that can efficiently adapt to changing antenna characteristics, as well as sensor fusion techniques that can enable monitoring behaviors of a driver in an automobile. Furthermore, this thrust is investigating methods for remote attestation of IoT edge devices, security aware dynamic power management and secure power IC design through EMI regulation. Additionally, this thrust includes research towards MEMS-based gas sensing, high-resolution TEM imaging-based reliability analysis of novel devices, as well as design of efficient temperature sensors for thermal performance characterization in power ICs.

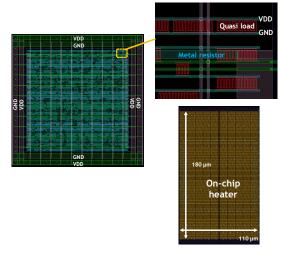

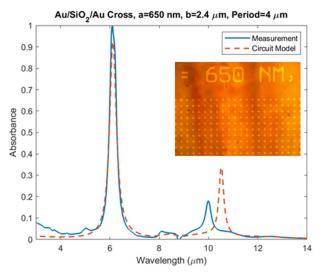

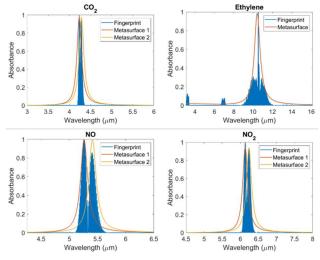

Figure 3. (Top left) PLL incorporating 4.3-GHz VCO using programmable array of cross-coupled NMOS transistors for automated low phase noise calibration (K. K. O, University of Texas at Dallas), (Top center) Plan-view SEM images of gate finger damage with surface discharge lines (M. Kim, University of Texas at Dallas), (Top right) Powered ESD-caused latch-up in a commercial MCU, attributed to reverse body bias scheme used for power reduction. (E. Rosenbaum, University of Illinois Urbana Champaign), (Bottom left) Electromagnetic emission-based malware analysis (S. Mukhopadhyay, Georgia Institute of Technology), (Bottom center) Custom designed components for AC power cycling test setup (B. Akin, University of Texas at Dallas) (Bottom right) Experimental study of meta-surface IR absorbers for MEMS-based gas sensing (J. Sebastian Gomez Diaz, University of California, Davis).

(Thrust leader: Ali Niknejad, UC Berkeley)

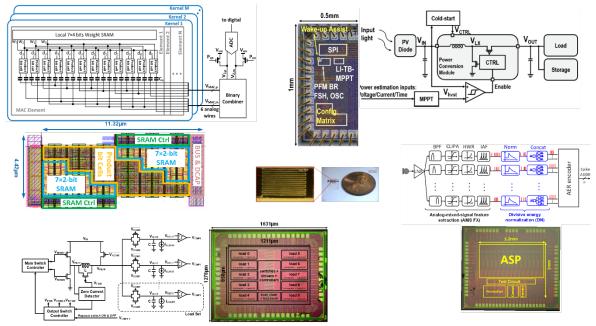

Figure 4. The TxACE Energy Efficiency thrust has diverse tasks ranging from power management to analog mixedsignal AI, and devices and packaging solutions for the implementation of modern systems in increasingly smaller form factors.

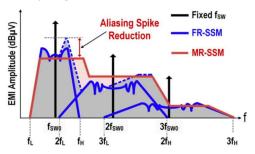

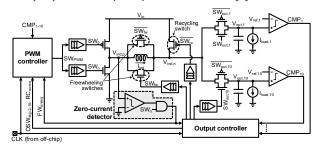

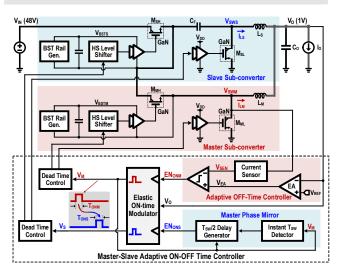

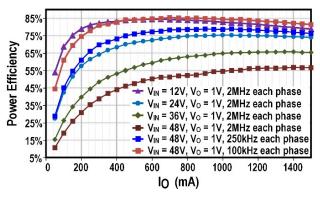

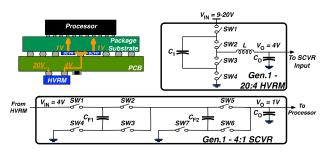

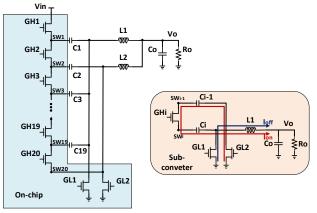

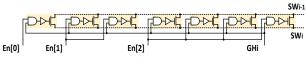

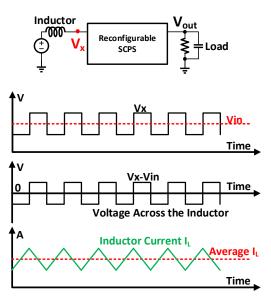

The TxACE Energy and Efficiency thrust is committed to tackling energy efficiency in electronic systems, spanning from traditional power management, all the way to the emerging fields of low power machine learning/AI for edge computing and applications to IoT sensor nodes. The power management research forms the foundation of the center and tackles important issues of efficiency in complex system applications, for example in digital multi-core systems that use single inductor multiple output (SIMO) DC-DC converters, addressing modeling and simulation and optimization of performance (voltage ripple, EMI) using non-linear control, mixed-signal techniques, digital signal processing, and adaptive algorithms. Tasks investigate non-conventional hybrid architectures and integration strategies for applications in computing, large-ratio conversion from 48V down to 1V and below, EV traction, and charging applications. Many of the solutions employ mixed-signal techniques, exploiting digital trends, and utilize novel scaling friendly analog architectures to improve the control and expand the flexibility of the overall system.

### FUNDAMENTAL ANALOG CIRCUITS RESEARCH

(Thrust leader: Pavan Hanumolu, U. of Illinois Urbana-Champaign)

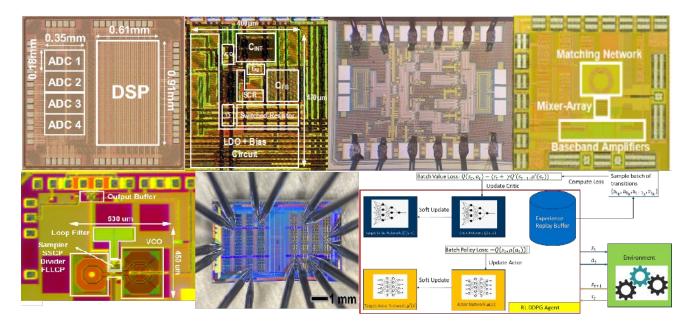

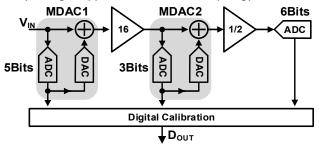

The research in this thrust focuses on cross-cutting areas in analog and mixed signal circuits which impact all of the TxACE application areas (Energy Efficiency, Public Safety, Security, and Health Care). The research includes the design of a wide variety of analog-to-digital converters, communication links, low-power crystal oscillators, I/O circuits, noise reduction techniques, new amplifier topologies suitable for use in nano-scale CMOS, development of CAD tools, and testing of integrated circuits.

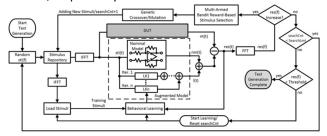

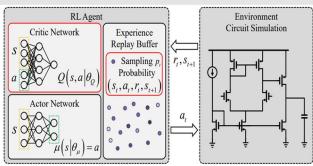

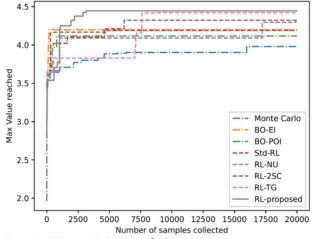

Figure 5. (Top row: from left) Speech-recognition using adaptive beamforming and feature extraction (M. Flynn, University of Michigan), RC-based temperature compensated 100MHz frequency reference (P. Hanumolu, University of Illinois), 170 - 260 GHz wideband power amplifier (A. Babakhani, UCLA), PLL with post-fabrication phase noise reduction capability (K. O, UT Dallas) (Bottom row: from left) Low-jitter sub-sampling PLL (A. Niknehad, UC Berkeley), On-chip online learning circuit with STT-MRAM (J. Friedman, UT Dallas), Sample-efficient reinforcement learning approach for analog circuit optimization (P. Li, UCSB)

#### **TXACE ANALOG RESEARCH FACILITY**

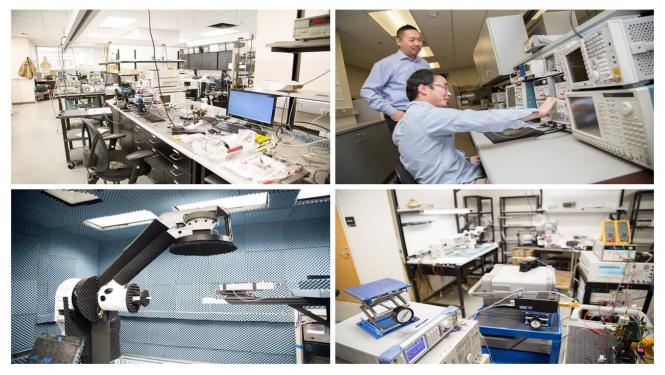

The centralized group of laboratories of the Texas Analog Center of Excellence dedicated to analog engineering research and training occupy a ~ 8000-ft2 area on the 3rd floor of the Engineering and Computer Science North building (Figure 6). The facility includes RF and THz, Integrated System Design, Embedded Signal Processing, and Analog & Mixed Signal laboratories as well as CAD/Design laboratory structured to promote collaborative research. The unique instrumentation capability includes network analyses and linearity measurements up to 325 GHz, spectrum analysis up to 120 THz, and cryo-measurements down to 2°K. The Center also added a pulsed multiple harmonic load and source pull measurement set up (up to 60 GHz for the third harmonic) and a 325-GHz antenna measurement set up. The close proximity of researchers in an open layout enables natural interaction and compels sharing of knowledge and instrumentation among the students and faculty. The TxACE analog research facility is one of the best equipped electronics laboratories. The laboratory is available for use by TxACE researchers and industrial partners all over the world.

Figure 6. TxACE Analog Research Facility

#### **RESEARCH PROJECTS AND INVESTIGATORS**

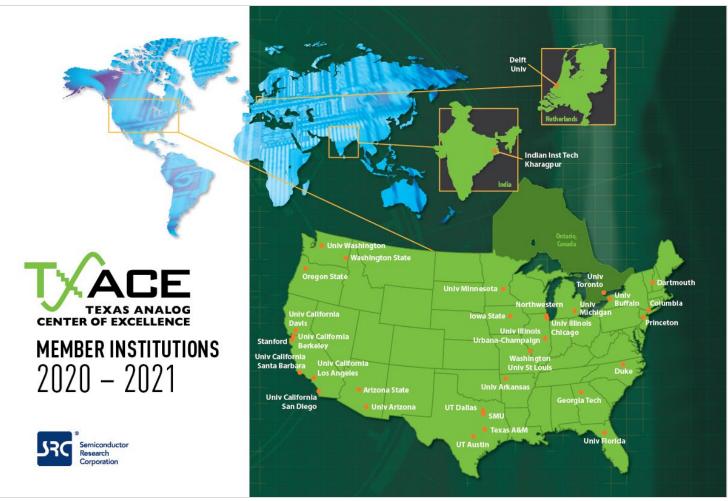

The Texas Analog Center of Excellence (TxACE) is the largest university analog technology center in the world. Table 1 lists the current principal investigators of the 89 tasks from 33 academic institutions funded by TxACE. Four universities (SMU, Texas A&M, UT Austin, UT Dallas) are from the state of Texas. 29 are from outside of Texas. Three (Delft University of Technology, Indian Institute of Tech. Kharagpur, and University of Toronto) (Figure 7) are from outside of the US. Of the 74 investigators, 23 are from Texas. During the past year, the Center supported 167 Ph.D., 23 M.S., and 11 B.S. students. 23 Ph.D. and 3 M.S. degrees were awarded to the TxACE students.

| Investigator  | Institution                         | Investigator | Institution                         | Investigator       | Institution            |

|---------------|-------------------------------------|--------------|-------------------------------------|--------------------|------------------------|

| B. Akin       | UT/Dallas                           | J. Gu        | Northwestern U.                     | N. Maghari         | UT/Dallas              |

| N. Al-Dhahir  | UT/Dallas                           | P. Gui       | SMU                                 | K. Makinwa         | Delft University       |

| D. Allstot    | UT/Dallas                           | A. Hanson    | UT/Austin                           | Y. Makris          | UT/Dallas              |

| R. Ayyanar    | Arizona State U.                    | P. Hanumolu  | UIUC                                | Y. Mengüç          | Oregon State U.        |

| A. Babakhani  | UC/Los Angeles                      | A. Hazra     | Indian Institute of Tech. Kharagpur | P. Mercier         | UC/San Diego           |

| B. Bakkaloglu | Arizona State U.                    | R. Henderson | UT/Dallas                           | U. Moon            | Oregon State U.        |

| S. Bhunia     | U. Florida                          | D. Heo       | Washington<br>State University      | S.<br>Mukhopadhyay | Georgia Tech.          |

| D. Blaauw     | U. Michigan                         | S. Hoyos     | TEES                                | B. Murmann         | Stanford U.            |

| P. Blanche    | U. Arizona                          | J. Hu        | TEES                                | F. Najm            | U. Toronto             |

| C. Busso      | UT/Dallas                           | M. lyer      | UT/Dallas                           | A. Niknejad        | UC/Berkeley            |

| A. Chatterjee | Georgia Tech.                       | M. Johnston  | Oregon State U.                     | К. О               | UT/Dallas              |

| D. Chen       | Iowa State U.                       | C. Kim       | U. Minnesota                        | S. Ozev            | Arizona State U.       |

| Y. Chen       | Duke U.                             | M. Kim       | UT/Dallas                           | S. Palermo         | TEES                   |

| Z. Chen       | U. Arkansas,<br>Fayetteville        | H. Le        | UC/San Diego                        | S. Pamarti         | UC/Los Angeles         |

| P. Dasgupta   | Indian Institute of Tech. Kharagpur | G. Lee       | UT/Dallas                           | P. Pande           | Washington<br>State U. |

| J. Doppa      | Washington<br>State University      | H. Lee       | UT/Dallas                           | G. Rincón-Mora     | Georgia Tech.          |

| W. Eisenstadt | U. Florida                          | M. Lee       | UT/Dallas                           | R. Rohrer          | SMU                    |

| M. Flynn      | U. Michigan                         | P. Li        | UC/Santa<br>Barbara                 | E. Rosenbaum       | UIUC                   |

| J. Friedman   | UT/Dallas                           | J. Liu       | UT/Dallas                           | A. Sanyal          | U. at Buffalo          |

| R. Geiger     | Iowa State U.                       | H. Lu        | UT/Dallas                           | V. Sathe           | U. of<br>Washington    |

| S. Gómez-Díaz | UC/Davis                            | D. Ma        | UT/Dallas                           | K. Sengupta        | Princeton U.           |

| Investigator      | Institution          | Investigator | Institution     | Investigator | Institution                 |

|-------------------|----------------------|--------------|-----------------|--------------|-----------------------------|

| M. Seok           | Columbia U.          | D. Sylvester | U. Michigan     | M. Torlak    | UT/Dallas                   |

| H. Shichijo       | UT/Dallas            | Y. Takashima | U. Arizona      | A. Trivedi   | U. Illinois,<br>Chicago     |

| J. Stauth         | Dartmouth<br>College | G. Temes     | Oregon State U. | X. Zhang     | Washington U.,<br>St. Louis |

| M.<br>Swaminathan | Georgia Tech.        | S. Thompson  | U. Florida      |              |                             |

Table 1. Principal Investigators (May 2020 through April 2021)

Figure 7. Member Institutions of Texas Analog Center of Excellence

### SUMMARY OF RESEARCH PROJECTS

The 89 research projects funded through TxACE during 2020-2021 are listed in Table 2 below by the Semiconductor Research Corporation task identification number.

|    | Task     | Thrust | Title                                                                                                                                     | Task Leader                        | Institution                               |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------|

| 1  | 2712.006 | EE     | Robust, Efficient All-Digital SIMO Converters for<br>Future SOC Domains                                                                   | Sathe, Visvesh                     | University of<br>Washington               |

| 2  | 2712.011 | FA     | Robust Reliable and Practical High Performance<br>References in Advanced Technologies                                                     |                                    |                                           |

| 3  | 2712.012 | EE     | EDAC and DCDC-Converter Co-Design for Addressing<br>Robustness Challenges in Emerging Architectures                                       | Seok, Mingoo                       | Columbia University                       |

| 4  | 2712.013 | SS     | Reconfigurable MM-Wave Tx Architecture and<br>Antenna Interface with Active Impedance Synthesis<br>in Multi-Port Node-Conjugated Combiner | Sengupta, Kaushik                  | Princeton University                      |

| 5  | 2712.14  | FA     | Leveraging CMOS Scaling in High Performance ADCS                                                                                          | Maghari, Nima                      | University of Florida                     |

| 6  | 2712.015 | SS     | Area-Efficient On-Chip System-Level IEC ESD<br>Protection for High Speed Interface ICs                                                    | Chen, Zhong                        | U. of Arkansas,<br>Fayetteville           |

| 7  | 2712.017 | SS     | Mitigating Reliability Issues in Analog Circuits                                                                                          | Kim, Chris                         | U. of Minnesota                           |

| 8  | 2712.018 | SS/EE  | Test Techniques to Approach Several Defect-per-<br>billion for Power ICs                                                                  | Eisenstadt, William                | University of Florida                     |

| 9  | 2712.020 | EE     | Low-Power Mostly Digital Time-Domain Delta-Sigma<br>ADCs for IoT                                                                          | Sanyal, Arindam                    | University at Buffalo                     |

| 10 | 2712.021 | SS     | Distributed Silicon Circuits and Sensors in 3D-Printed<br>Systems for Wearable IoT Sensors                                                | Johnston, Matthew<br>Mengüç, Yiğit | Oregon State<br>University                |

| 11 | 2712.022 | SS     | Intrinsic Identifiers for Database-Free Remote<br>Authentication of IoT Edge Devices                                                      | Bhunia, Swarup<br>Trivedi, Amit    | U. of Florida and<br>U. Illinois, Chicago |

| 12 | 2712.024 | EE     | A System-In-Package Platform for Energy Harvesting<br>and Delivery for IoT Edge Devices                                                   | Mukhopadhyay, S.<br>Madhavan, S.   | Georgia Tech.                             |

|    | Task     | Thrust | Title Task Leader                                                                                                                                              |                         | Institution              |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|

| 13 | 2712.025 | FA     | Reduction of Low Frequency Noise Impact in Nano-<br>Scale CMOS Circuits                                                                                        | O, Kenneth              | UT/Dallas                |

| 14 | 2712.026 | SS     | Fault Characterization and Degradation Monitoring of SiC Devices                                                                                               | Akin, Bilal             | UT/Dallas                |

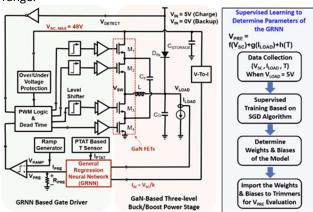

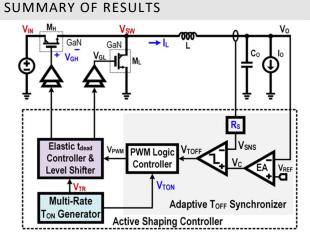

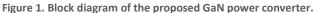

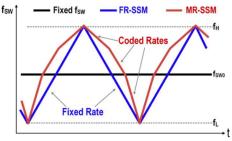

| 15 | 2712.027 | EE     | Gate Driving Techniques and Circuits for<br>Automotive-Use GaN Power Circuits                                                                                  | Ma, D. Brian            | UT/Dallas                |

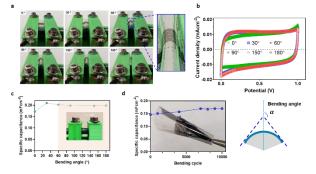

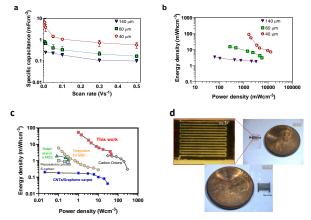

| 16 | 2712.028 | EE     | High Performance Micro-supercapacitor on a Chip<br>Based on a Hierarchical Network of Nitrogen Doped<br>Carbon Nanotube Sheets Supported MnO2<br>Nanoparticles | Lee, Gill               | UT/Dallas                |

| 17 | 2712.029 | SS     | Novel Super-resolution and MIMO Techniques for<br>Automotive and Emerging Radar Applications                                                                   | Torlak, Murat           | UT/Dallas                |

| 18 | 2712.031 | FA     | Adaptive Trimming and Testing of Analog/RF<br>Integrated Circuits (ICs)                                                                                        | Makris, Yiorgos         | UT/Dallas                |

| 19 | 2810.002 | SS/EE  | Security-Aware Dynamic Power Management for<br>System-on-Chips                                                                                                 | Mukhopadhyay,<br>Saibal | Georgia Tech.            |

| 20 | 2810.003 | EE     | Integrated Voltage Regulator Management for<br>System-on-Chip Architectures Zhang, Xuan                                                                        |                         | Washington<br>University |

| 21 | 2810.005 | FA/SS  | Circuit Design for ESD and Supply Noise Mitigation                                                                                                             | Rosenbaum, Elyse        | UIUC                     |

| 22 | 2810.006 | EE     | Combating Unprecedented Efficiency, Noise and<br>Frequency Challenges in Modern High Current<br>Integrated Power Converters                                    | Ma, D. Brian            | UT/Dallas                |

| 23 | 2810.007 | FA     | Fully Integrated Phase Noise Cancellation<br>Techniques                                                                                                        | Niknejad, Ali           | UC/Berkeley              |

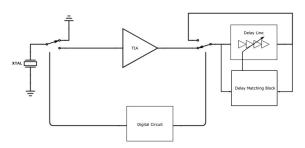

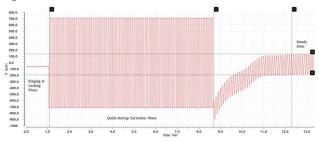

| 24 | 2810.008 | EE     | Circuit Techniques for Fast Start-Up of Crystal<br>Oscillators                                                                                                 | Pamarti, Sudhakar       | UCLA                     |

| 25 | 2810.009 | EE/FA  | Mixed-Signal Building Blocks for Ultra-low Power<br>Wireless Sensor Nodes Blaauw, David U.                                                                     |                         | U. of Michigan           |

| 26 | 2810.010 | EE     | GS/s ADC Based Cycle-to-Cycle Closed-Loop Adaptive<br>Smart Driver for High-Performance SiC/GaN Power<br>Devices                                               | Gui, Ping               | SMU                      |

|    | Task     | Thrust | Title                                                                                                                                                          | Task Leader                         | Institution                            |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|

| 27 | 2810.011 | EE     | Micro-Power Analog-to-Digital Data Converters for<br>Sensor Interfaces                                                                                         | Temes, Gabor                        | Oregon State<br>University             |

| 28 | 2810.012 | EE     | NPSense - Nano-Power Current Sensing                                                                                                                           | Makinwa, Kofi                       | Delft University                       |

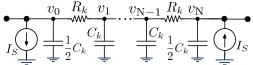

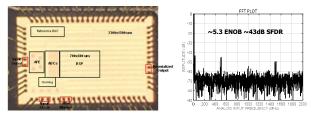

| 29 | 2810.013 | FA     | Frequency-Domain ADC-Based Serial Link Receiver<br>Architectures for 100+Gb/s Serial Links                                                                     | Palermo, Samuel<br>Hoyos, Sebastian | TEES                                   |

| 30 | 2810.014 | SS     | Deep Learning Solutions for ADAS: From Algorithms<br>to Real-World Driving Evaluations                                                                         | Busso, Carlos<br>Al-Dhahir, Naofal  | UT/Dallas                              |

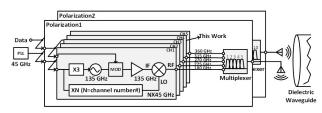

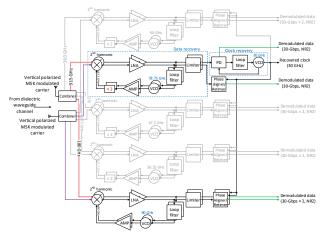

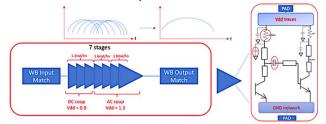

| 31 | 2810.015 | FA     | Demonstration of 120-Gbps Dielectric Waveguide<br>Communication Using Frequency Division<br>Multiplexing (FDM) and Polarization Division<br>Multiplexing (PDM) | O, Kenneth                          | UT/Dallas                              |

| 32 | 2810.016 | SS     | Condition Monitoring of Industrial/Automotive Drive<br>Components through Leakage Flux                                                                         | Akin, Bilal                         | UT/Dallas                              |

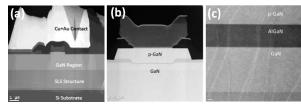

| 33 | 2810.017 | SS     | Reliability Study of E-mode GaN HEMT Devices                                                                                                                   | Kim, Moon<br>Shichijo, Hishashi     | UT/Dallas                              |

| 34 | 2810.018 | FA     | Transition Design for High Data Rate Links at<br>Submillimeter Wave Frequencies                                                                                | Henderson,<br>Rashaunda             | UT/Dallas                              |

| 35 | 2810.019 | FA     | Design Automation for Coverage Management in<br>Analog and Mixed-Signal SOCs                                                                                   | Dasgupta, Pallab<br>Hazra, Aritra   | Indian Institute of<br>Tech. Kharagpur |

| 36 | 2810.020 | FA     | Analog/Mixed-Signal RF Circuit Time Domain<br>Sensitivity and Its Applications                                                                                 | Rohrer, Ronald                      | SMU                                    |

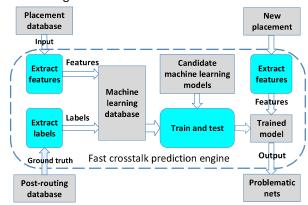

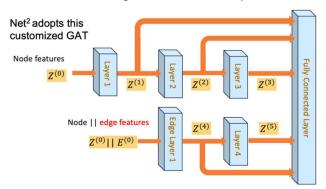

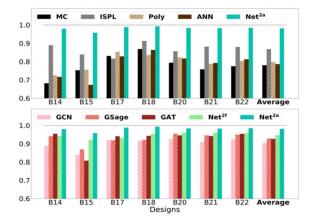

| 37 | 2810.021 | SS     | A Collaborative Machine Learning Approach to Fast<br>and High-Fidelity Design Prediction                                                                       | Hu, Jiang<br>Chen, Yiran            | TEES and<br>Duke University            |

| 38 | 2810.022 | SS     | A Collaborative Machine Learning Approach to Fast<br>and High-Fidelity Design Prediction                                                                       | Chen, Yiran<br>Hu, Jiang            | Duke University<br>And TEES            |

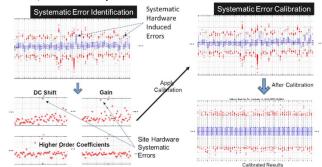

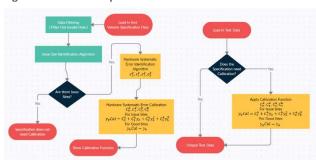

| 39 | 2810.023 | SS     | Machine Learning Driven Automatic Mixed-Signal<br>Design Verification-Validation for Automotive<br>Applications                                                | Chatterjee, Abhijit                 | Georgia Tech.                          |

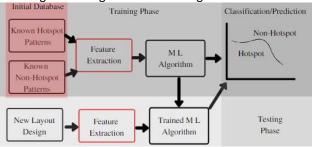

| 40 | 2810.025 | SS     | Machine Learning-Based Layout Analysis and Netlist<br>Optimization for Defect Tolerance and Design<br>Robustness to Process Imperfections and Variations       | Makris, Yiorgos                     | UT/Dallas                              |

|    | Task     | Thrust | Title Task Leade                                                                                                       |                  | Institution                 |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|

| 41 | 2810.027 | SS     | Measurement and Modeling of Stress/Strain on<br>Analog Transistor and Circuit<br>Parameters                            | Thompson, Scott  | University of Florida       |

| 42 | 2810.028 | FA     | Robust ATE Multi-Site HW Design to Enable Effective<br>Analog Performance Testing in Analog-Mixed-Signal<br>(AMS) SoCs | Chen, Degang     | lowa State University       |

| 43 | 2810.029 | FA     | 170GHz – 260GHz Wideband PA and LNA Design in<br>Silicon                                                               | Babakhani, Aydin | UCLA                        |

| 44 | 2810.030 | FA     | Neural Network Recognition & On-Chip Online<br>Learning with STT-MRAM                                                  | Friedman, Joseph | UT/Dallas                   |

| 45 | 2810.031 | FA     | Development and Asssessment of Machine Learning<br>Based Analog and Mixed-Signal Verification                          | Li, Peng         | UC/Santa Barbara            |

| 46 | 2810.032 | EE     | DRIVR: A Digital, Re-configurable, Unified Clock-<br>Power (UniCaP) Fabric for Energy-Efficient SoCs                   | Sathe, Visvesh   | University of<br>Washington |

| 47 | 2810.033 | FA     | Interleaved Noise-Shaping SAR ADCs for High-Speed<br>and High-Resolution                                               | Flynn, Michael   | U. of Michigan              |

| 48 | 2810.034 | EE     | Always-on Keyword Spotting based on Analog-<br>Mixed-Signal Computing Hardware                                         |                  |                             |

| 49 | 2810.035 | EE     | Computationally Controlled Integrated Voltage<br>Regulators                                                            | Sathe, Visvesh   | University of<br>Washington |

| 50 | 2810.036 | FA     | Highly Stable Integrated Frequency References                                                                          | Hanumolu, Pavan  | UIUC                        |

| 51 | 2810.037 | FA     | High-performance Ringamp-based ADCs                                                                                    | Moon, Un-Ku      | Oregon State<br>University  |

| 52 | 2810.038 | SS     | Extreme Temperature Digital, Analog, and Mixed-<br>Signal Circuits (ET-DAMS)                                           | Kim, Chris       | U. of Minnesota             |

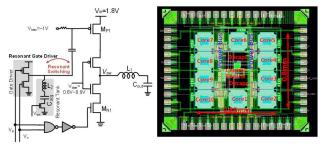

| 53 | 2810.039 | EE     | Integrated D(-D)( Converter with Resonant Gate (Gullie)                                                                |                  | Northwestern<br>University  |

| 54 | 2810.040 | EE     | Hybrid/Resonant Sc Converters with Integrated Lc<br>Resonator for High-Density Monolithic Power<br>Delivery            | Stauth, Jason    | Dartmouth College           |

|    | Task     | Thrust | Title                                                                                                                                                      | Task Leader              | Institution                 |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|

| 55 | 2810.041 | SS     | ESD Protection for IO Operating at 56 Gb/s and<br>Beyond                                                                                                   | Rosenbaum, Elyse         | UIUC                        |

| 56 | 2810.042 | EE     | Digitally Enhanced High Efficiency, Fast Settling<br>Augmented DCDC Converters                                                                             | Bakkaloglu, Bertan       | Arizona State<br>University |

| 57 | 2810.043 | FA     | Analog Optimization Hybridizing Designer's Intent<br>and Machine Learning                                                                                  | Li, Peng                 | UC/Santa Barbara            |

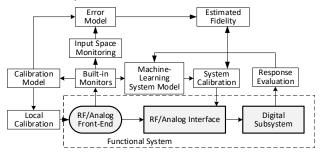

| 58 | 2810.044 | FA     | Hierarchical Characterization and Calibration of RF/Analog Circuits Using Lightweight Built-in Sensors                                                     | Ozev, Sule               | Arizona State<br>University |

| 59 | 2810.046 | SS     | Generating Current Constraints for Electromigration<br>Safety                                                                                              | Najm, Farid              | University of Toronto       |

| 60 | 2810.047 | SS     | Architecture and DfT methods for improving life<br>time reliability and functional safety of electronic<br>circuits and systems out of application context | Chen, Degang             | Iowa State University       |

| 61 | 2810.048 | SS     | Characterization and Mitigation of Electromigration<br>Effects in Advanced Technology Nodes                                                                | Kim, Chris               | U. of Minnesota             |

| 62 | 2810.049 | EE     | 1-W Battery-Charging CMOS Buck Regulator                                                                                                                   | Rincón-Mora,<br>Gabriel  | Georgia Tech.               |

| 63 | 2810.050 | SS     | Integrating Metasurfaces and MEMS for Gas Sensing                                                                                                          | Gómez-Díaz,<br>Sebastian | UC Davis                    |

| 64 | 2810.051 | SS/EE  | High Gain DC-DC Converter for EV Traction System                                                                                                           | Ayyanar, Raja            | Arizona State<br>University |

| 65 | 2810.052 | FA     | TI PLM as Hologram Generator for HUD (Head Up<br>Display) and AR                                                                                           | Blanche, Pierre          | University of Arizona       |

| 66 | 2810.053 | FA     | TI PLM to Advanced Lidar and Display Systems                                                                                                               | Takashima, Yuzuru        | University of Arizona       |

| 67 | 2810.054 | SS     | Reconfigurable AC Power Cycling Setup and Plug-in<br>Condition Monitoring Tools for High Power IGBT and<br>SiC Modules                                     | Akin, Bilal              | UT/Dallas                   |

| 68 | 2810.055 | SS/EE  | EMI-Regulated Secure Automotive Power ICs                                                                                                                  | Ma, D. Brian             | UT/Dallas                   |

|    | Task     | Thrust | Title                                                                                                                                                              | Task Leader                               | Institution                    |

|----|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|

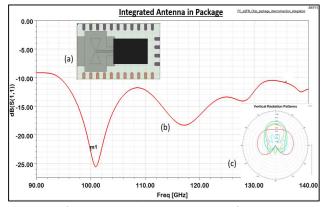

| 69 | 2810.056 | FA     | Millimeter Wave Packaging Research - Antenna in<br>Package                                                                                                         | lyer, Devan                               | UT/Dallas                      |

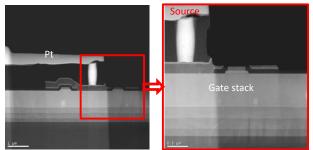

| 70 | 2810.057 | SS     | Reliability Study of E-mode GaN HEMT Devices by AC<br>TDDB and High Resolution TEM                                                                                 | Kim, Moon<br>Shichijo, Hishashi           | UT/Dallas                      |

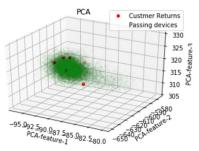

| 71 | 2810.058 | SS/FA  | Machine Learning-Based Overkill/Underkill<br>Reduction in Analog/RF IC Testing                                                                                     | Makris, Yiorgos                           | UT/Dallas                      |

| 72 | 2810.060 | FA     | Intelligent, Learning ADCs for the Post Figure-of-<br>Merit World                                                                                                  | Flynn, Michael                            | U. of Michigan                 |

| 73 | 2810.061 | EE     | Two-Stage Vertical Power Delivery and Management for Efficient High-Performance Computing                                                                          | Le, Hanh-Phuc<br>Mercier, Patrick         | UC/San Diego                   |

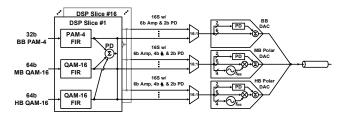

| 74 | 2810.062 | FA     | Multi-Carrier DAC-Based Transmitter Architectures<br>for 100+Gb/s Serial Links                                                                                     | Palermo, Samuel<br>Hoyos, Sebastian       | TEES                           |

| 75 | 2810.063 | FA     | Analog and Digital Assist Techniques to Improve<br>Mixed-Signal Performance                                                                                        | Sylvester, Dennis<br>Blaauw, David        | U. of Michigan                 |

| 76 | 2810.064 | SS     | Characterization and Tolerance of Ageing in<br>Integrated Voltage Regulators                                                                                       | Mukhopadhyay,<br>Saibal                   | Georgia Tech                   |

| 77 | 2810.065 | EE/SS  | Power-Efficient and Reliable 48-V DC-DC Converter<br>with Direct Signal-to-Feature Extraction and DNN-<br>Assisted Multi-Input Multiple-Output Feedback<br>Control | Seok, Mingoo                              | Columbia University            |

| 78 | 2810.066 | SS     | Demonstrably Generalizable Compact Models of ESD<br>Devices                                                                                                        | Rosenbaum, Elyse                          | UIUC                           |

| 79 | 2810.067 | EE     | Highly Efficient Extreme-Conversion-Ratio Buck<br>Hybrid Converters                                                                                                | Pande, Partha<br>Heo, Deuk<br>Doppa, Jana | Washington State<br>University |

| 80 | 2810.068 | EE     | Active EMI Filtering with Switch-Mode Amplifier for<br>High Efficiency                                                                                             | Hanson, Alex                              | UT Austin                      |

| 81 | 2810.070 | SS     | Early and Late Life Failure Prediction Methods for<br>Analog and Mixed-Signal Circuits                                                                             | Kim, Chris                                | U. of Minnesota                |

|    | Task     | Thrust | Title                                                                                                                                     | Task Leader                        | Institution                |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|

| 82 | 2810.071 | FA     | Accurate Compact Temperature Sensors for Thermal<br>Management of High Performance Computing<br>Platforms Geiger, Randall<br>Chen, Degang |                                    | Iowa State University      |

| 83 | 2810.072 | EE     | AI/ML Edge Hardware for Ultra-reliable Wireless<br>Networks                                                                               | Allstot, David                     | Oregon State<br>University |

| 84 | 2810.073 | EE     | AI/ML Edge Hardware for Ultra-reliable Wireless<br>Networks                                                                               | Makris, Yiorgos                    | UT/Dallas                  |

| 85 | 2810.074 | SS     | Thermal Performance Characterization and<br>Degradation Monitoring of LDMOS based Integrated<br>Power IC with On-Die Temperature Sensors  | Akin, Bilal                        | UT/Dallas                  |

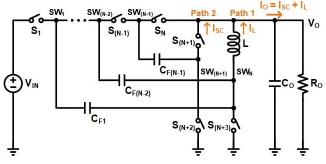

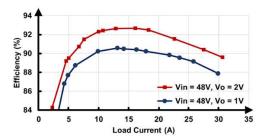

| 86 | 2810.075 | EE     | Hybrid Step-Down DC-DC Converters with Large<br>Conversion Ratios for 48V Automotive Applications                                         | Lee, Hoi<br>Liu, Jin               | UT/Dallas                  |

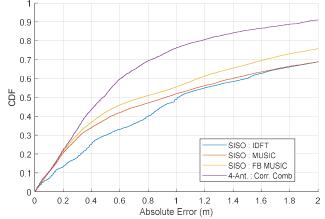

| 87 | 2810.076 | FA     | High Precision Positioning Techniques Based on<br>Multiple Technologies and Frequency Bands                                               | Al-Dhahir, Naofal<br>Torlak, Murat | UT/Dallas                  |

| 88 | 2810.077 | SS     | Increasing Lifetime of Nano-Scale CMOS Circuits                                                                                           | O, Kenneth                         | UT/Dallas                  |

| 89 | 2810.078 | EE     | Programmable Mixed-Signal Accelerator for DNNs with Depthwise Separable Convolution Layers                                                | Murmann, Boris                     | Stanford University        |

# Table 2: Funded research projects at TxACE by SRC task identification number (FA: Fundamental Analog, EE: Energy Efficiency, SS: Safety, Security and Health Care)

### ACCOMPLISHMENTS

In the past year, TxACE has made significant research progress. Table 3 summarizes the number of publications and inventions resulting from the TxACE research during May 2020 to April 2021, while Table 4 lists the major research accomplishments for the Center during the period. The TxACE researchers have published 41 conference papers and 30 journal papers. They have also made 4 invention disclosure, filed 5 patent applications, and were granted 4 patents. The list of publications is included as Appendix I. Following the tabulation, brief summaries of each project are provided.

#### Table 3. TxACE number of publications (May 2020 through April 2021)

| Conference<br>Papers | Journal Papers | Invention<br>Disclosures | Patents Filed | Patents Granted |

|----------------------|----------------|--------------------------|---------------|-----------------|

| 41                   | 30             | 4                        | 5             | 4               |

| Category                            | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

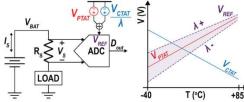

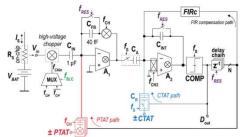

| Energy<br>Efficiency<br>(Circuits)  | A ±2A fully-integrated current sensor with a 20-m $\Omega$ on-chip shunt (resistor) has<br>been demonstrated. It uses an energy-efficient hybrid sigma-delta ADC with an<br>FIR-DAC and consumes only 1.4 $\mu$ A, a 3× improvement on the state-of-the-art. A<br>tunable analog temperature-compensation scheme allows ±2A currents to be<br>digitized with 0.35% gain error from -40 to 85 ° C. A gain error of about 0.6% for<br>±15A currents was achieved with a 3-m $\Omega$ PCB shunt. The sensor occupies 1.6 mm <sup>2</sup><br>in 180-nm CMOS. (2810.012, K. Makinwa, TU Delft)        |

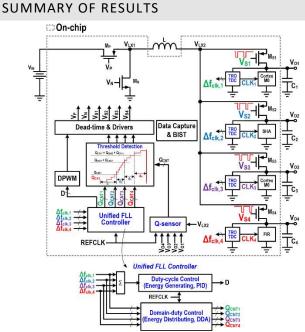

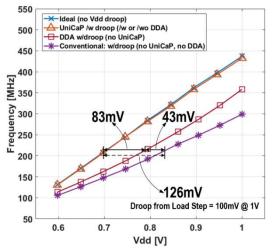

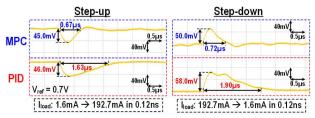

| Energy<br>Efficiency<br>(Circuits)  | A Single Inductor Multiple Output (SIMO) regulated SoC in 65-nm CMOS demonstrated two techniques that mitigate the prohibitive voltage droop and ripple margin problems of SIMO regulated domains. The first extends the Unified Clock and Power (UniCaP) adaptive clocking architecture to multiple domains and achieves 98% average voltage margin reduction. The second introduces Dynamic Droop Allocation, which concurrently analyzes charge delivery requirements and equalizes droop across all domains to reduce worst-case transient droop by 73%. (2810.032, V. Sathe, U. Washington) |

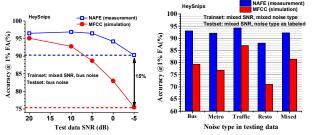

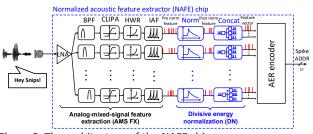

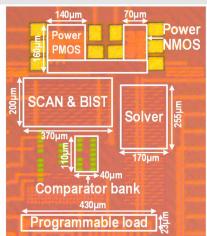

| Energy<br>Efficiency<br>(Circuits)  | Always-on keyword spotting (KWS) is essential for a voice-based user interface in<br>mobile and edge devices. This project uses the hybridization of analog-mixed-<br>signal and digital hardware and demonstrated a sub-600nW KWS system with<br>environmental noise and process variation robustness. The system incorporates a<br>5-layer spiking neural network (SNN) classifier having 650 neurons and 67,000<br>synapses fabricated in 65-nm CMOS. The SNN hardware demonstrates 7 to 1000X<br>reduced power consumption. (2810.034, M. Seok, Columbia)                                    |

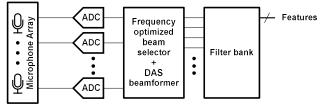

| Fundamental<br>Analog<br>(Circuits) | A compact, low-power microphone-to-spectrogram beamforming frontend processor for speech recognition is demonstrated by bit-stream processing of the outputs generated by an array of sigma-delta modulators that digitize microphone outputs. The prototype beamformer fabricated in a 40-nm CMOS process occupies an active area of 0.89mm <sup>2</sup> and improves speech recognition accuracy in noisy conditions from 64% to 90%. (2810.060, M. Flynn, U. Michigan)                                                                                                                        |

#### Table 4. Major TxACE Research Accomplishments (May 2020 through April 2021)

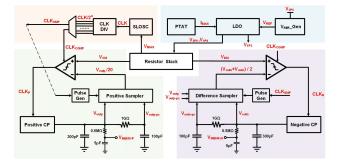

| Fundamental<br>Analog<br>(Circuits)              | High accuracy RC oscillator-based frequency reference is demonstrated by precise<br>and robust cancellation of the resistor temperature coefficient (TC) across the<br>process. Using a parallel combination of switched-resistors that are digitally<br>controlled by temperature-compensating pulse-density modulated sequences,<br>the output frequency's first- and second-order TCs are suppressed. A prototype<br>100MHz frequency reference fabricated in a 65-nm CMOS process achieved an<br>inaccuracy of 140ppm, 80ppm/V voltage sensitivity, 2.5ppm Allan deviation, and<br>1 $\mu$ W/MHz power efficiency. (2810.036, P. Hanumolu, UIUC) |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

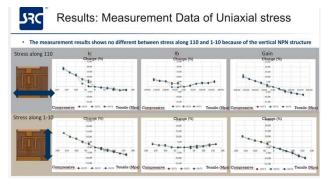

| Safety,<br>Security and<br>Health Care<br>(CADT) | Packaging of electronic devices introduces compressive biaxial stress and variable vertical stress due to silicon particles in the epoxy. The compressive biaxial stress (a common type in most commercial packages) increases intrinsic carrier concentration and electron mobility in npn transistors, both of which increases collector current. Tensile stress reduces the packaging effect to the collector current of npn transistors. (2810.027, S. Thomson, U. of Florida)                                                                                                                                                                   |

# Safety, Security and Health Care Thrust

| Category                                                                     | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Safety,<br>Security and<br>Health Care<br>(Systems)                          | The goal of this project is to demonstrate miniaturized infrared (IR) gas sensors (CO <sub>2</sub> , NO, NO <sub>2</sub> , Ethylene) operating at room temperature based on ultrathin meta-surfaces (MTSs) integrated within a nano-mechanical resonator system (NMEMS). The first set of meta-surfaces based on gold nano-resonators deposited on 200nm of SiO <sub>2</sub> provides almost 100% absorption at the desired wavelength with an FWHM $\approx$ 0.25µm or Q of ~20. The meta-surfaces will be integrated with NMEMS resonators to demonstrate a complete gas sensing system. (2810.050, S. Gómez-Díaz, UC Davis) |  |  |  |

| Safety,<br>Security and<br>Health Care<br>(CADT)                             | Packaging of electronic devices introduces compressive biaxial stress and variable<br>vertical stress due to silicon particles in the epoxy. The compressive biaxial stress<br>(a common type in most commercial packages) increases intrinsic carrier<br>concentration and electron mobility in npn transistors, both of which increase<br>collector current. Tensile stress reduces the packaging effect to the collector<br>current of npn transistors. (2810.027, S. Thomson, U. of Florida)                                                                                                                               |  |  |  |

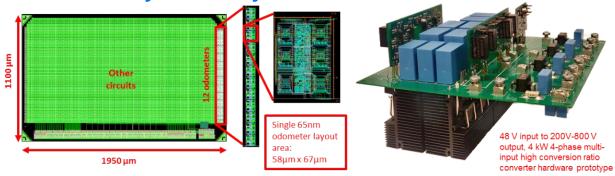

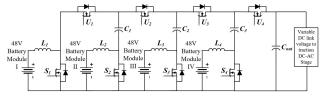

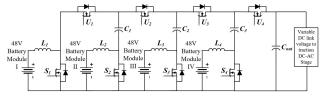

| Safety,<br>Security and<br>Health Care<br>Energy<br>Efficiency<br>(Circuits) | A high gain, wide output voltage range multi-input high gain DC-DC converter with<br>low voltage and current stress semiconductor devices has been developed.<br>Multiple low voltage battery packs are employed in cell balancing due to<br>independent charging-discharging of each battery module and increased safety for<br>EV traction system. The proposed concept has been verified through a hardware<br>prototype attaining a peak efficiency of 98.3 % at 48 V input to 400 V output at 2<br>kW. (2810.051, R. Ayyanar, Arizona State University)                                                                   |  |  |  |

## TASK 2712.013, RECONFIGURABLE MM-WAVE TX ARCHITECTURE AND ANTENNA INTERFACE WITH ACTIVE IMPEDANCE SYNTHESIS IN MULTI-PORT NODE-CONJUGATED COMBINER

KAUSHIK SENGUPTA, PRINCETON UNIVERSITY, KAUSHIKS@PRINCETON.EDU

#### SIGNIFICANCE AND OBJECTIVES

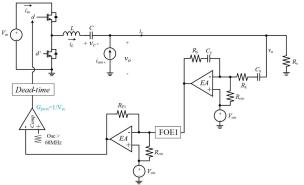

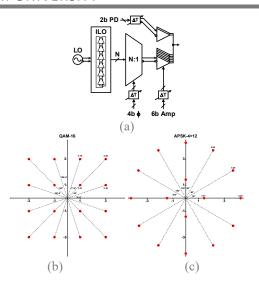

In this project, we demonstrated a generalized multiport approach for 1) Broadband VSWR-reconfigurable PA architecture with a multi-port DAC based topology (VLSI'19, TMTT Apr'20), 2) first mm-Wave Load Modulated Balanced Amplifier (LMBA) that aims broadband and back-off efficiency in the 5G bands (IMS'2020 **Best student paper 2<sup>nd</sup> prize,** TMTT paper in prep., patent filed).

#### **TECHNICAL APPROACH**

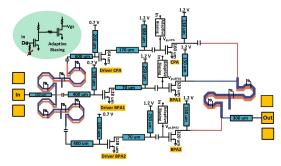

We proposed a generalized method of load pulling to overcome VSWR in a reconfigurable fashion between 26-40 GHz. For the LMBA, we presented the first mmWave load modulated balanced PA architecture with adaptive biasing for enhanced linearity.

#### SUMMARY OF RESULTS

We demonstrated the first mm-Wave load-balanced PA with a transformer-based hybrid at input and output to allow wideband power combining and achieve high isolation with PA control for load-modulation and back-off efficiency enhancement across 30-40 GHz.

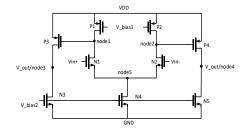

Figure 1. Schematic of the broadband VSWR-tolerant PA architecture in 65-nm CMOS operating across 26-40 GHz.

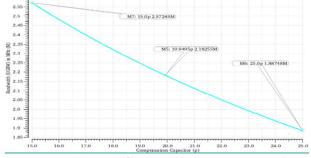

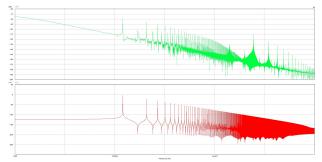

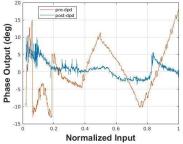

To overcome the compressive behavior of an LMBA and enhance linearity, an integrated adaptive biasing is integrated on-chip allowing superior ACLR performance across 30-40 GHz (Fig. 1). Under CW excitation, the twostage LMBA demonstrates output power of 18.5-20 dBm, output drain efficiency >30% across 30-40 GHz (Fig. 2). The modulation capabilities of LMBA are tested using a 64 QAM signal with a data rate of 6Gbps wherein PA demonstrates EVM of -26.4 dB and ACLR of -29 dBc at an average output power of 10.6 dBm (Fig. 2).

Figure 2. Linearity measurements of LMBA across 30-40 GHz along with drive ups at 33,36 and 40 GHz. EVM and ACLR vs average output power for a 16/64 QAM signal at 33 GHz. 16QAM and 64QAM constellations and spectra.

Spectrally-agile transmitters between 30-100 GHz should be investigated.

#### Keywords: mmWave, PA, load modulation, 5G

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, NXP

#### MAJOR PAPERS/PATENTS

[1] C.R.Chappidi, T.Sharma, Z.Lu, and K.Sengupta, "Load Modulated Balanced mm-Wave CMOS PA with Integrated Linearity Enhancement for 5G applications," *IMS 2020* (*Best student paper 2<sup>nd</sup> prize*).

[2] Kaushik Sengupta and Chandrakanth Chappidi, "Load modulated balanced mm-Wave PA architecture," provisional patent filed.

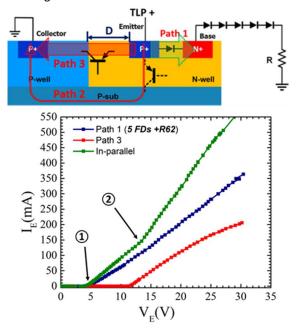

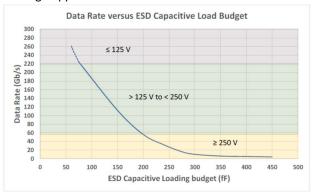

Area-efficient, low-capacitance, on-chip system-level IEC ESD protection solutions for high-speed interface ICs will be designed, fabricated, characterized, and optimized based on the dual-diode ESD protection structure.

#### TECHNICAL APPROACH

To reduce the total ESD device areas and the parasitic capacitance, our approach is to utilize the inherent parasitic PNP structure in the high-side ESD diode as a parallel path to shunt the ESD discharge current. The key for this approach is to adjust the characteristics of substrate PNP structures by optimizing the layout such that the triggering and ESD clamping voltage of the parasitic PNP structure is within the specific ESD protection window.

#### SUMMARY OF RESULTS

Various ESD protection diodes with finger-type and island-type layouts were fabricated in a UMC65-nm process and characterized to compare the ESD behaviors (e.g., current carrying efficiency, parasitic capacitance, and leakage current). The leakage current and parasitic capacitance of both island-type and finger-type diodes are small such that they can be used for the high-speed applications. The island-type layout design can achieve higher failure current through the inherent parasitic PNP structure compared to the finger-type counterpart with the same area. The high-level metal routing helps reduce the total parasitic capacitance of ESD diodes.

The proposed ESD diode with the optimized parasitic PNP structure is connected with external "forward diodes" as the primary ESD cell (shown in Figure 1). This test structure of ESD protection path is used to demonstrate the improved ESD performance with optimized ESD diode. Three TLP (Transmission-Line Pulse) measurements were carried out in sequence: (1) Individual Path 1 represents the "high-side forward diode + primary ESD cell"; (2) individual lateral parasitic PNP (labeled "Path 3") with base floating; (3) Path 1 and Path 3 (in-parallel) configuration. Figure 1 also presents the TLP I-V characterization results. Using 5 forward biased diodes in series with a  $62\Omega$  resistor as a primary ESD cell, it shows that V<sub>t1</sub> of Path 1 and Path 3 is 5V and 11V, respectively. When the optimized ESD path (i.e., "High-side diode + Parasitic PNP+ Primary ESD Cell" configuration) turns on under the ESD event, the point (2) in Fig. 1 indicates the turn-on of the lateral parasitic PNP (Path 3) which is around 11V, and it dominates over vertical PNP (Path 2) to help shunt current in parallel with Path 1. It verifies the operation of our proposed ESD cell with optimized parasitic PNP.

Moreover, the displacement current induced by the parasitic capacitance on the power supply or the current injected by the primary ESD cell may affect the ESD behavior of the inherent parasitic substrate PNP during power-on condition. Three comparison groups (a. the direction of the injected current, b. the location of the current injection point, and c. the level of injected current) were designed and tested to evaluate the effects.

Figure 1. The testing configuration of the proposed P+/N-well diode connected with external "forwards" as primary ESD cell for the demonstration and TLP characterization results.

#### Keywords: ESD, PNP, IEC, TCAD, Current injection

#### INDUSTRY INTERACTIONS

Texas Instruments

#### MAJOR PAPERS/PATENTS

H. Wang, et al, "Area-efficient Dual-diode with Optimized Parasitic Bipolar Structure for Rail-based ESD Protections", Microelectronics Reliability, in press.

Z. Chen, M. Ali, and H. Wang., "ESD Self-protection of Output Circuitry Using Substrate Bipolar Structure," provisional patent filed.

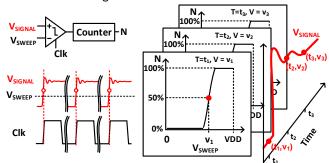

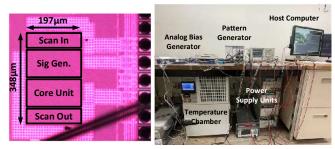

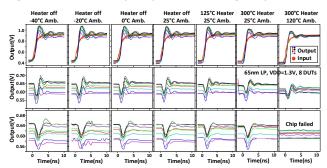

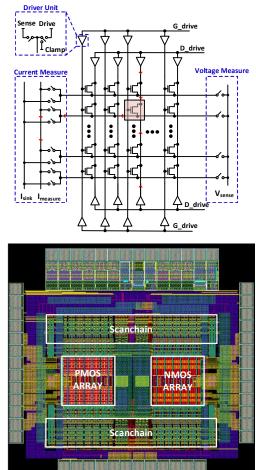

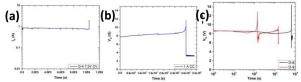

An on-chip analog waveform sampling system was demonstrated in a 65-nm process focusing on extreme temperature step response measurements. Amplifier output waveforms were measured under different temperatures ranging from -40 degrees Celsius ambient temperature to 300 degrees Celsius heater temperature.

#### **TECHNICAL APPROACH**

We demonstrated a fully integrated measurement system for characterizing analog signal waveforms at extremely high temperatures. We employed the subsampling technique, where the signal level of a repetitive high-speed analog signal is detected by sweeping a known reference voltage until the signal level is reached. The voltage sweep measurement is repeated while incrementing the time offset between the triggering clock and the sampling clock to reconstruct the full waveform. To raise the local circuit temperature without damaging the package and test board, we integrated a metal heater with serpentine wires above the circuit under test.

#### SUMMARY OF RESULTS

Fig. 1 shows the operating principle of the sub-sampling technique used in this work. For a repetitive analog signal, we obtained the sweep voltage versus occurrence curve at each sampling time. If sweep voltage is below the analog signal voltage, then the occurrence is low, and vice versa. The 50% point represents the sampled voltage. The occurrence curve is recorded while incrementing the sampling time offset until the time window of interest is measured. The occurrence curves are stitched together to recreate the analog waveform.

Figure 1. On-chip sub-sampling of repetitive analog signals and waveform reconstruction method.

Fig. 2 shows the 65-nm test chip die photo and testing environment. Fig. 3 shows the characterization results of 8 amplifiers from the same chip at 1.3V. The input step voltage is switched from 0.4V to 0.9V. The 1.3V supply voltage used in the experiments is 100mV higher than the nominal voltage to allow more headroom during voltage overshoot events. We can see that the overshoot decreases slightly until 125°C but degrades significantly at 300°C. The slew rate increases with temperature at first but decreases for a heater temperature of 300°C and an ambient temperature of 120°C, likely due to the threshold voltage reduction being dominant compared to the mobility degradation. The settling time is generally longer below 0°C compared with room temperature and 300°C cases.

Figure 2. 65-nm test chip die photo and testing setup.

Figure 3. Device characterization array schematic.

**Keywords:** High temperature, amplifier response, on-chip heater, analog reliability, sub-sampling technique

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel

#### MAJOR PAPERS/PATENTS

[1] H. Yu, G. Park, and C.H. Kim, "Extreme Temperature Characterization of Amplifier Response Up to 300 Degrees Celsius Using Integrated Heaters and On-Chip Samplers", ESSCIRC, 2021 (to appear)

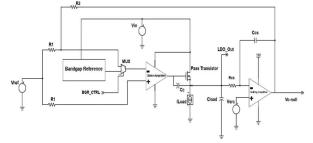

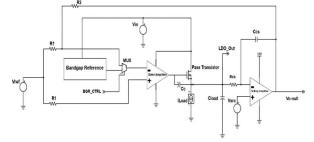

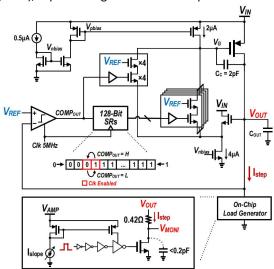

This work designed, simulated, and tested custom LDO and Buck Converter power ICs using additional bare-die test points to improve part failure rates. The goal was to test yield enhancement by culling power ICs with outlier subcircuit performance. Recent work characterized smallsignal LDO control loop gain using IC external pins.

#### **TECHNICAL APPROACH**

Researchers developed simulations of power ICs with internal IC test features for enhanced testing. These were used to determine subcircuit performance inside of 65-nm CMOS LDOs and Buck Converters. Analyses and simulations of custom-designed LDO and Buck converters were performed to prove these new test concepts. A 65nm CMOS LDO test IC and a Buck converter test IC were fabricated and tested. The functional LDO IC was used to characterize on-chip power IC control loop gain and phase response and develop fast methods to do this on the ATE.

#### SUMMARY OF RESULTS

For the final six months of this project, TI proposed the new goal of devising a method of quickly testing existing LDO's. The prior work was limited to the observation of the LDO IC with advanced test features and external control loop components. Modern LDO's use internal compensation techniques with Miller capacitors or cascode capacitors to provide LDO control compensation.

In this work, researchers focused on analyzing a generic Miller compensated LDO IC design with good simulated line regulation, load regulation, PSSR, and a unity gain frequency of 2.2 MHz with a phase margin of -67°. Cascode compensated LDOs yield similar results. The generic Miller compensated LDO was placed in a Servoloop test as shown in Figure 1. This configuration can be easily realized on the load board and used during ATE test.

Figure 1. A Generic Miller Compensated LDO inside a servoloop for test simulations.

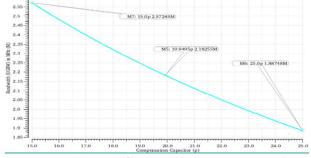

Servo-loop test simulations were performed. The servo-loop measurement simulations of DC gain were compared with the extracted DC gain from the Cadence Spectre software using stability analysis. The simulations agreed closely. The Miller capacitor compensated LDO showed an inverse linear control-loop cutoff variation with the Miller capacitor value (proportional to 1/Cc).

A goal of this year's work was to test the LDO frequency response in 20mS. The Servo-loop test can characterize the gain bandwidth curve using three frequency points and be used to extrapolate loop cutoff frequency and loop capacitance. Figure 2 shows simulations of generic Miller compensated LDO control-loop bandwidth versus compensation capacitor value. A nominal compensation capacitor of 20 pF yields a control loop bandwidth of 2.2 MHz. If the compensation capacitor is lowered to 15pF then the loop bandwidth is 2.6 MHz and if the compensation capacitor value is raised 25pF the loop bandwidth is 1.9 MHz. So, one could determine a bad onchip compensation capacitor value by injecting three signals into the servo-loop, 20% above the nominal cutoff, at the cutoff frequency, and 20% below the LDO cutoff frequency and measuring the loop gain.

Figure 2. Simulations of Generic Miller Compensated LDO inside a test servo-loop.

Integrating a compensated servo-loop for a small signal test on chip is feasible. An integrated servo-loop would require a small area of the LDO chip compared to the other LDO subcircuits.

Keywords: Test, Analog, Power, LDO, Buck Converter

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] Anurag Tulsiram and William R. Eisenstadt, "Design for Testability of Low Dropout Regulators," IEEE VLSI Test Symposium 2021, April 26-28, 2021, Virtual Interactive Live Event.

### TASK 2712.021, DISTRIBUTED SILICON CIRCUITS AND SENSORS IN 3D-PRINTED SYSTEMS FOR WEARABLE IOT SENSORS MATTHEW L. JOHNSTON, OREGON STATE UNIVERSITY, JOHNSTOM@OREGONSTATE.EDU YIĞIT MENGÜÇ, OREGON STATE UNIVERSITY

#### SIGNIFICANCE AND OBJECTIVES

There is an emerging set of applications that require stretchable, compliant electronics – including wearable devices, instrumented fabrics, and soft robots with distributed sensors and computation. In this project, we are working to demonstrate a fundamentally new method for the fabrication of stretchable, 3D-printed objects containing distributed sensors and silicon ICs.

#### **TECHNICAL APPROACH**

Developing stretchable electronics faces two primary challenges: integration of active semiconductor devices in elastic substrates and providing stretchable, conductive interconnects. In this project, we combine 3D printing of liquid metal materials and silicone rubber with PCB fabrication techniques to build solid 3D objects with electronic components distributed throughout. Silicon integrated circuits, used for computation, sensing, and actuation, will be connected through liquid metal conductors confined to 3D microfluidic channels. Through additive, layer-by-layer construction, electronic devices can be inserted and connected throughout the 3D structure. We will also develop compact models for the interconnects, which will be used to design adaptable front-end circuits for stretchable interconnect interfaces.

#### SUMMARY OF RESULTS

For this project, we have demonstrated progress (Fig. 1) in printing multi-layer stretchable circuits using discrete components, extended strain testing of liquid metal paste material, and developed a compact modeling framework for stretchable interconnects. Specific outcomes have included:

- Demonstrated printing of sensors and analog and digital interconnects using discrete active and passive components [1,2].

- Extended testing of stretchable interconnects, demonstrating <5% change in resistance over 100,000 stretch cycles at 50% strain (1.5X) [4].

- Compact modeling framework for Cadencecompatible simulation of stretchable interconnects under static and dynamic strain conditions [3].

- Printed antenna structures for future integration into stretchable circuits with wireless communication.

- Developed both 3D-printing and stencil-based fabrication methods for stretchable circuits [5, 6].

Figure 1. Printed stretchable circuits (top) with active and passive components [1]; 100,000 cycle strain data (middle); printed stretchable devices such as antennas (bottom) are also feasible using the liquid metal paste materials and methods.

# **Keywords:** Stretchable electronics, 3D printing, wearable devices, packaging, sensor interfaces

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, IBM

#### MAJOR PAPERS/PATENTS

[1] C. Votzke, U. Daalkhaijav, Y. Mengüç, and M.L. Johnston, "3D-printed liquid metal interconnects for stretchable electronics," *IEEE Sensors Journal*, vol. 19, no. 10, pp. 3832 - 3840, 2019.

[2] C. Votzke et al., "Highly-stretchable biomechanical strain sensor using printed liquid metal paste," *IEEE BioCAS*, 2018.

[3] K. Clocker et al., "Compact modeling of stretchable printed liquid metal electrical...," *IEEE FLEPS*, 2019.

[4] C. Votzke et al., "Electrical characterization of stretchable printed liquid metal interconnects under repeated cyclic loading," *IEEE FLEPS*, 2019.

[5] C. Votzke et al., "Stenciled liquid metal paste for robust stretchable electrical interconnects," *IEEE FLEPS*, 2021.

[6] C. Votzke, et al., "Auger-based 3D printing of stretchable liquid metal paste...," *IEEE FLEPS*, 2021.

### TASK 2712.022, INTRINSIC IDENTIFIERS FOR DATABASE-FREE REMOTE AUTHENTICATION OF IOT EDGE DEVICES SWARUP BHUNIA, UNIVERSITY OF FLORIDA, SWARUP@ECE.UFL.EDU AMIT RANJAN TRIVEDI, UNIVERSITY OF ILLINOIS AT CHICAGO

#### SIGNIFICANCE AND OBJECTIVES

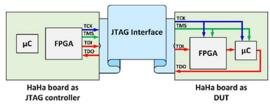

We have developed a low-power CMOS framework and testchip for non-parametric density estimation of timeseries and anomaly detection in low-likelihood samples. We have also introduced a current and delay signaturebased authentication technique for IC and PCB integrity verification utilizing the onboard JTAG structure that protects against counterfeiting/cloning/in-field tampering attacks.

#### **TECHNICAL APPROACH**

We have fabricated a testchip to learn non-parametric statistics of streaming sensor data using kernel density estimation (KDE) technique. KDE is realized using Gaussian kernel functions. The anomaly detection framework allows for programming parameters such as sliding-window length, kernel standard deviation, and likelihood threshold to ensure efficient detection. Meanwhile, through physical measurements, we observe that the supply current in a PCB heavily fluctuates depending on the overall in-circuit switching activities in the boundary scan chain of the PCB, which is utilized to authenticate ICs, and PCBs concurrently and detect in-field tampering

#### SUMMARY OF RESULTS

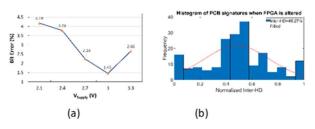

In the PCB verification technique, we deploy a custom hardware platform that consists of two chips (an FPGA and a microcontroller) in its boundary-scan architecture (BSA). Using the industry standard, we transmit test data into BSA, and meanwhile, perform hands-on current measurements at both chip level and PCB level over 20 boards to generate device-specific signatures that demonstrate high uniqueness, robustness, and randomness properties. The block diagram of the systemlevel connection is depicted in Figure 1. The experiments are run over 20 different PCBs of the same kind at five different supply voltage levels. Figure 2(a) illustrates the percentage bit errors from every operating point, demonstrating the robustness of the generated signatures. Finally, we conduct intentional alteration experiments by replacing onboard FPGA to replicate the scenario of PCB tampering. The results (Figure 2(b)) indicate the successful detection of the intentional modifications introduced to the boundary-scan chain of the PCB. Figure 3(a) shows the testchip to learn the nonparametric statistics of time-series data in an unsupervised setting. Figure 3(b) shows the measured densities of Gaussian statistics with different means. Further, the test setup to characterize the multi-modal densities is being developed for detecting side-channel fault-injection attacks on crypto-hardware.

Figure 1. Block diagram of IC and PCB level connections.

Figure 2. (a) V<sub>supply</sub> variation results; (b) inter-Hamming distance results for intentional alteration experiments.

Figure 3. (a) Test-chip for no parametric density estimation; (b) density estimation of Gaussian statistics with different means.

**Keywords:** Kernel density estimation, non-parametric, anomaly detection, authentication, Hamming, JTAG, PUF

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, IBM

#### MAJOR PAPERS/PATENTS

[1] S. Bhunia et al., U.S. Patent, Filed with U. Florida, App. 17/097,446.

[2] S.D. Paul et al., "SILVerIn: Systematic Integrity Verification of Printed Circuit Board Using JTAG Infrastructure," ACM JETC.

In this project term, real-time condition monitoring circuits are proposed and developed based on switching transient to detect device degradation and monitor junction temperature. Experimental results are carried out to verify the accuracy of the proposed junction temperature measurement with aging compensation.

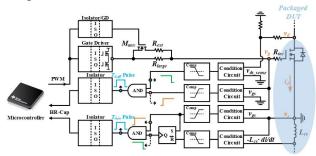

#### **TECHNICAL APPROACH**

In this study, a widely adopted power cycling test is used to induce thermal-mechanical and electro-thermal stresses to SiC MOSFETs. To evaluate the device's aging impact on its switching performance, a double pulse tester platform is developed and employed. Both turn-on and turn-off transients are collected over the lifetime of the device under test (DUT). Based on the observed aging precursor, an aging detection circuit is designed and developed. To achieve on-line condition monitoring for real-time aging detection, a junction temperature ( $T_j$ ) compensation technique is proposed and developed.

#### SUMMARY OF RESULTS

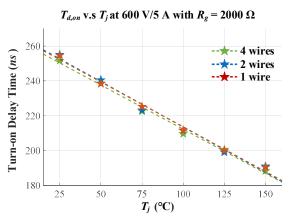

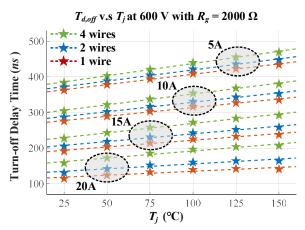

To investigate the device's switching performance shift throughout aging, a double pulse test circuit is built, and the turn-on delay ( $T_{d,on}$ ) shift of a commercial SiC MOSFET is tested at different  $T_j$ . It is observed that as  $T_j$  goes up, the threshold voltage drops linearly, and the turn-on delay time decreases accordingly. Meanwhile, device aging causes retardation in  $T_{d,on}$  as indicated at 0 and 6000 power cycles. On the contrary, it suggests a decreased turn-off delay ( $T_{d,off}$ ) over aging.

The proposed aging detection circuit diagram is shown in Fig. 1.

Figure 1. Circuit diagram of real-time aging detection circuit.

To mimic device degradation patterns in realistic cases, the DUT is decapsulated and its power-source bond wires are cut off from the leads. The experimental results of  $T_{d,on}$ , and  $T_{d,off}$  measurements are shown in Fig. 2 and Fig. 3, respectively. The mismatch of the read  $T_j$  through  $T_{d,on}$ and  $T_{d,off}$  are caused by the device's aging. By capturing this  $T_j$  mismatch shift over aging, the temperature impact on aging precursors is compensated and real-time aging detection is achieved.

Figure 2. Measured turn-on delay at different state-of-health.

Figure 3. Measured turn-off delay at different state-of-health.

Keywords: aging detection, reliability, SiC MOSFETs

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

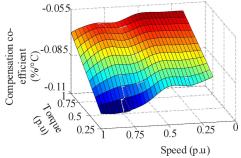

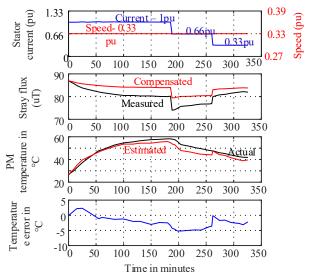

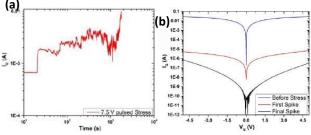

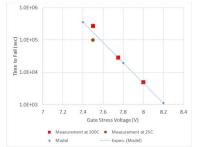

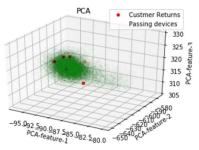

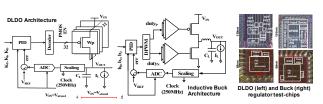

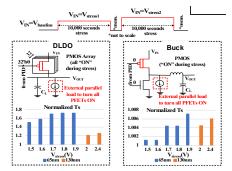

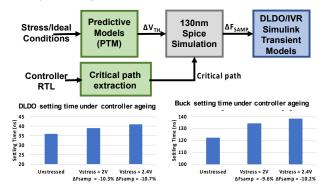

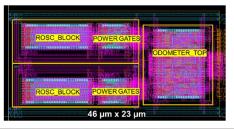

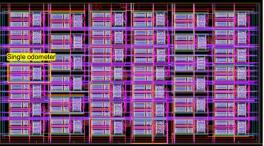

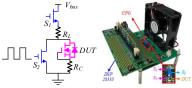

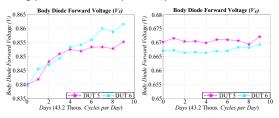

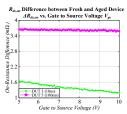

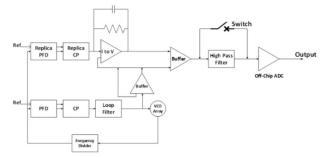

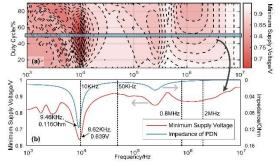

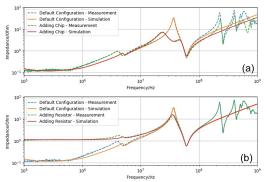

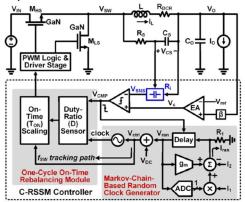

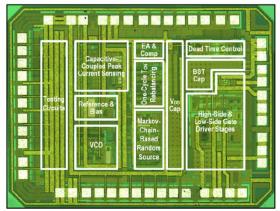

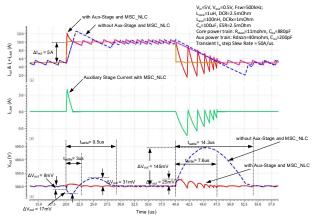

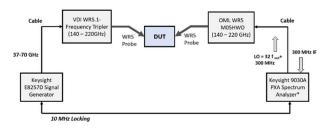

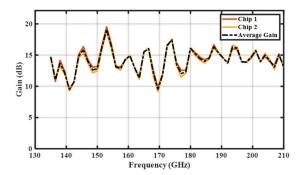

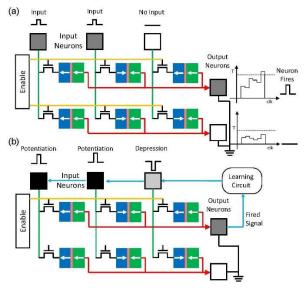

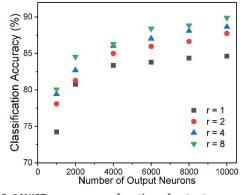

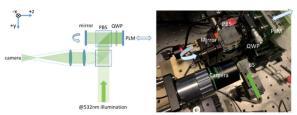

[1] F. Yang, S. Pu, C. Xu and B. Akin, "Turn-on Delay Based Real-Time Junction Temperature Measurement for SiC MOSFETs With Aging Compensation," in IEEE Transactions on Power Electronics, vol. 36, no. 2, pp. 1280-1294, Feb. 2021.