# TEXAS ANALOG CENTER OF EXCELLENCE ANNUAL REPORT 2009 – 2010

# OUR MISSION

The Texas Analog Center of Excellence seeks to create fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

## **OUR RESEARCH THRUSTS**

- Safety & Security

- Health Care

- Energy Efficiency

- Fundamental Analog Circuits Research

# **TxACE 2009-2010 ANNUAL REPORT**

Analog and mixed signal integrated circuits engineering is both a major opportunity and a major challenge. It is an opportunity because of the increasing importance of analog integrated circuits in electronic systems and the emergence of new applications. It is a challenge because of the inherent difficulty of the art. The creation of advanced wireless technology and sophisticated sensing and imaging devices depends on the availability of engineering talent for analog research and development. The Texas Analog Center of Excellence (TxACE) was established to help overcome the challenges and translate these opportunities into economic benefits for the participants and society. Support for TxACE has been provided through a collaboration of the State of Texas, Texas Instruments, the Semiconductor Research Corporation, the University of Texas System and the University of Texas at Dallas.

As the second year of TxACE operation closed, the center has much to be proud of. An ambitious research program is in place and beginning to yield results. The research tasks are being organized into four research thrust areas: Healthcare, Safety and Security, Energy Efficiency and Fundamental Analog. The scope of investigation extends from circuits operating at DC through terahertz, data converters that sample at tens of mega-samples/sec to tens of giga-samples/sec, AC-to-DC and DC-to-DC converters working at microwatts to watts, energy harvesting circuits, protein and DNA sensors and many more. Significant improvement on existing mixed signal systems and exciting new applications based on this circuit research are anticipated.

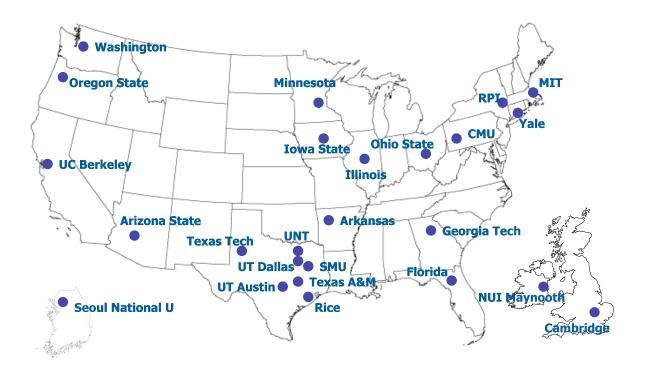

Graduate students who have been exposed to hands-on innovative research are forming the leading edge of a flow of analog talent into industry. Close collaboration with and responsiveness to industry needs provides focus to the educational experience. TxACE researchers and engineers are ready to perform. Located at The University of Texas at Dallas, TxACE has rapidly grown from a concept to a dynamic working reality. On the basis of the number of principal investigators and funding, it is now the largest analog center in the world. **Figure 1** shows the location of academic institutions including three international universities. A

3

significant portion of the program involves Texas Universities and Texas industry in order to enhance the local economy.

The new TxACE analog laboratory just coming online provides a working environment that promotes collaboration among researchers. The laboratory includes capabilities for device and circuit characterization at high frequencies well beyond that used in present day commercial electronics, opening up the door for novel circuit research for new applications and markets.

Figure 1: TxACE Member institutions

#### DIRECTOR'S MESSAGE

This second year of TxACE operation has matured and focused all facets of the center. Our objective is to lead analog research and education that can create new economic opportunities by improving analog and mixed signal technology, education, research and manufacturing. We are pleased to see our efforts beginning to show results. A flow of graduating analog engineering talent has been established and is entering the workplace. Individual research efforts herald the entry of innovative products into the marketplace. The process of technology transfer is underway.

At the close of the 2009-2010 period construction of TxACE laboratories and design facilities was completed, and the equipment is being installed. TxACE high frequency circuit characterization tools will help lower a critical barrier for advancing millimeter and sub-millimeter integrated circuit technology. These capabilities are a global asset, and plans are being formulated to provide access to the laboratories to TxACE members and others in a collaborative framework. The research and organizational structure of the center has been defined. Additionally, critical leadership positions have been filled. We are grateful to those who have stepped up to serve.

TxACE is now an international center that is the largest for analog research in the world on the basis of funding and the number of principal investigators (68 principal investigators from 26 academic institutions). A majority of the leading analog researchers in the United States are participating in the center. Seven schools (Rice, SMU, Texas A&M, Texas Tech, The University of North Texas, UT Austin, UT Dallas) are from Texas. Three (Seoul National University, Cambridge University, National University of Ireland, Maynooth) are from outside the United States.

Presently the center supports 73 graduate students (49 from Texas universities and 24 from outside of Texas). During the past year nine PhD and three MS degrees were awarded to TxACE students.

Despite being in existence for only two years, as documented in this report, TxACE can report significant achievements. This of course could not have happened without the support of TxACE's principal investigators and students as well as the support of the State of Texas, UT Dallas, Texas Instruments Inc. and Semiconductor Research Corp. I am proud of the TxACE team, and I am looking forward to a new year with greater research accomplishments and impact.

Kenneth K. O, Director TxACE Texas Instruments Distinguished Chair The University of Texas at Dallas

#### **MESSAGE FROM UT DALLAS**

Analog technology has existed in the shadow of digital technology for far too long, but the Texas Analog Center of Excellence is succeeding in changing that.

It is doing so through both research and education.

The research component speaks for itself: More than \$10 million in funding for directed research tasks performed by 68 principal investigators at 26 academic institutions. But the education component is equally important.

The majority of electrical engineering students have long specialized in digital electronics, but as the use of digital has grown, the need for analog of course has grown. But analog is growing at several times the rate of digital, and as a result analog engineers are in great demand.

Many engineers find analog more rewarding to work with than digital, and TxACE is helping to convey the excitement of analog technology to students. The numbers alone are impressive: TxACE projects have so far involved nearly 100 students in four countries.

But what those students mean for the future is more important still. They are the ones who will become analog engineers in industry, developing technology that will improve our lives in myriad ways. And they will pass along their enthusiasm for analog engineering to the next generation of students and engineers.

TxACE is to be congratulated for an outstanding start, and I look forward to seeing what great technology, students and engineers it produces in the years ahead.

Mark W. Spong

Dean, Erik Jonsson School of Engineering and Computer Science Lars Magnus Ericsson Chair in Electrical Engineering Excellence in Education Chair The University of Texas at Dallas

#### **MESSAGE FROM SEMICONDUCTOR RESEARCH CORPORATION**

The Texas Analog Center of Excellence has made strong progress since its creation just two years ago.

Under the direction of Kenneth K. O, TxACE has quickly become an influential resource for analog research and development, coordinating and supporting work that directly contributes to addressing the world's needs in key areas, including health care, energy, and safety and security.

But that's just the beginning.

- With the creation of a core laboratory facility, TxACE's influence will grow, and it will complement its distributed research approach with centralized resources available to researchers from various institutions using a collaborative framework.

- With TxACE's demonstrated success at bringing a methodical approach to analog research, we fully expect funding support for TxACE to expand in years ahead.

- As research continues, I am confident we will soon begin seeing real-world applications of TxACE-generated technology all around us.

Two years ago, Texas Gov. Rick Perry hailed TxACE as the sort of investment that is essential to strengthen growing industries and bolster the economy. TxACE has exceeded expectations, and I'm confident there is more to come from the growing number of researchers whose combined talents TxACE has succeeded in harnessing.

Larry W. Sumney, President and CEO Semiconductor Research Corporation

#### **BACKGROUND & VISION**

For the past 20 years semiconductor electronics was dominated by digital logic. This led to the digital revolution that we are all familiar with, affecting things from computational power to high-definition digital television. For the next 20 years, analog and mixed signal semiconductor technology is expected to drive progress as electronics continues to bridge the gap between the analog real world and the digital information infrastructure. In just the period from 2005 to 2007, the analog semiconductor market grew from \$30 billion to \$50 billion! High performance analog technology is a unique segment of the semiconductor electronics business. It requires special skills in both design and process that reside in the United States.

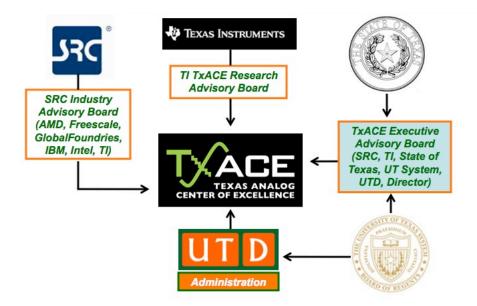

To lead this change, in particular to lead analog technology education, research, commercialization, manufacturing and job creation, the Texas Analog Center of Excellence was formally announced by Texas Gov. Rick Perry in October 2008 as a \$16 million collaboration of the Semiconductor Research Corp., the State of Texas through its Texas Emerging Technology Fund, Texas Instruments, Inc., The University of Texas System and UT Dallas (see **Figure 2**). The center seeks to accomplish these objectives by creating fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

#### **CENTER ORGANIZATION**

The Texas Analog Center of Excellence is guided by agreements established with the center sponsors. The advisory boards identify the research needs and select research tasks in consultation with the center leadership. **Figure 2** diagrams the relationship of TxACE to the members of the sponsoring collaboration.

Figure 2: TxACE organization relative to the sponsoring collaboration

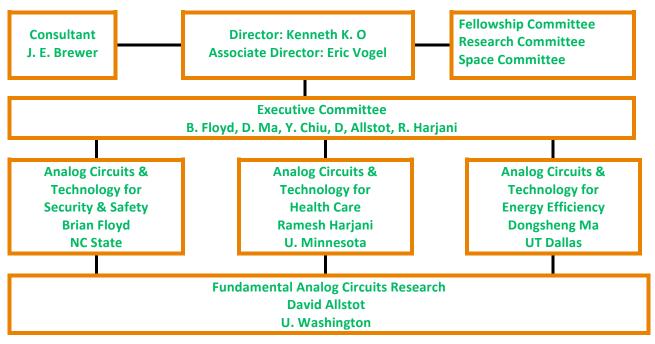

The internal organization of the center is structured to flexibly perform the research mission while not detracting from the educational missions of the University. **Figure 3** identifies the elements of the organization. The TxACE Director is Kenneth K. O and the Associate Director is Eric Vogel. The center research is arranged into four thrusts that comply with the mission of the Center: Safety and Security, Health Care, Energy Efficiency and Fundamental Analog Circuits. The last thrust consists of vital research that cuts across more than one of the first three research thrusts. The thrust leaders are Brian Floyd of North Carolina State University for the safety and security thrust, Ramesh Harjani of the University of Minnesota for the health care thrust, Dongsheng Ma of UT Dallas for the energy efficiency thrust. The thrust leaders and Yun Chiu of UT Dallas form the executive committee. The committee along with the director

and associate director form the leadership team which works to improve the research productivity of center by increasing collaboration, better leveraging the diverse capabilities of principle investigators of the center, and lowering research barriers. The leadership team also identifies new research opportunities for consideration by the advisory boards.

Figure 3: TxACE organization for management of research

#### PUBLIC SAFETY AND SECURITY

#### (Thrust leader: Brian Floyd, NC State)

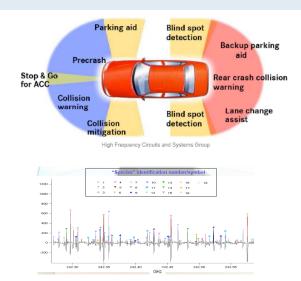

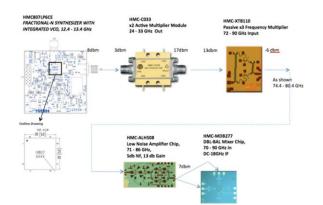

TxACE has awarded nearly \$1.5 million to researchers to develop analog technology that enhances public safety and security. The projects are intended to: 1) Enable a new generation of devices that can scan for harmful substances by researching 200-300-GHz silicon ICs for use in spectrometers and 2) Significantly reduce the cost of in-vehicle radar technology to improve automotive safety by researching circuit techniques that can improve manufacturing and lower test and packaging costs.

Figure 4: Millimeter wave radar to improve automobile safety and rotational spectrum around 300 GHz.

#### HEALTH CARE

#### (Thrust leader: Ramesh Harjani, University of Minnesota)

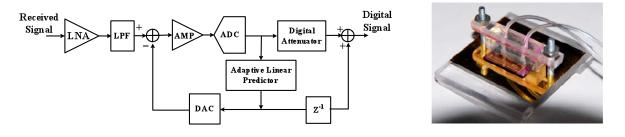

Analog and RF integrated circuit technology is the essential interface enabling the power, speed and miniaturization of modern digital microelectronics to be brought to bear on an array of medical issues, including medical imaging, patient monitoring, laboratory analyses, bio-sensing and new therapeutic devices. TxACE is working to identify and support analog circuit research challenges that have the potential to enable important health-related applications.

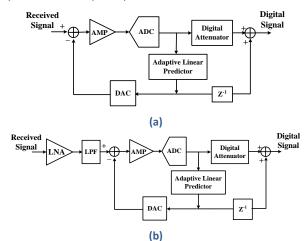

Figure 5: Receiver for ultrasound imaging based on adaptive data prediction with improved dynamic range (left). Micro-fluidic system for detecting protein markers using nanowire transistors (right).

#### ENERGY EFFICIENCY

#### (Thrust leader: Dongsheng Ma, UT Dallas)

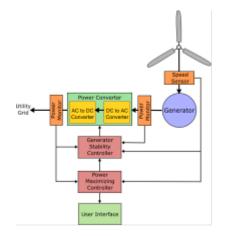

TxACE is committed to alleviate the global energy problem by improving the energy efficiency of electronic systems as well as by developing analog technologies that can make energy generation more efficient. The center is also working to energize and power long-lasting in-situ microscale devices such as wireless microsensors, biomedical implants and portable microelectronics.

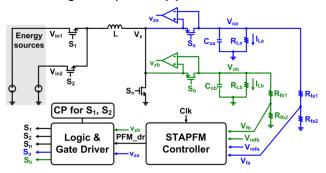

Figure 6: Electric generation system using wind (left). Single inductor multiple input and multiple output DC-DC converter (above).

#### FUNDAMENTAL ANALOG CIRCUITS RESEARCH

#### (Thrust leader: David Allstot, University of Washington)

Research in this thrust focuses on cross-cutting areas in analog circuits which impact all of the TxACE application areas (Energy Efficiency, Health Care, Public Safety and Security).

Fundamental analog circuits' research is crucial for the design of analog-to-digital converters and communication links, the development of CAD tools, and testing of high-speed circuits.

#### TXACE ANALOG RESEARCH FACILITY

UT Dallas has prepared a  $\sim$ 7,500 ft<sup>2</sup> area on the 3rd floor of the Engineering and Computer Science North building to form an enhanced centralized group of laboratories dedicated to analog engineering research and research training.

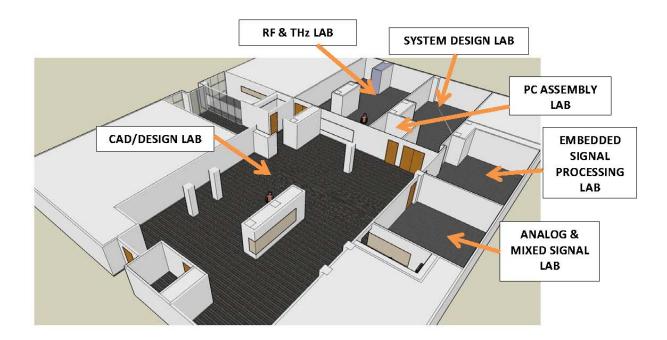

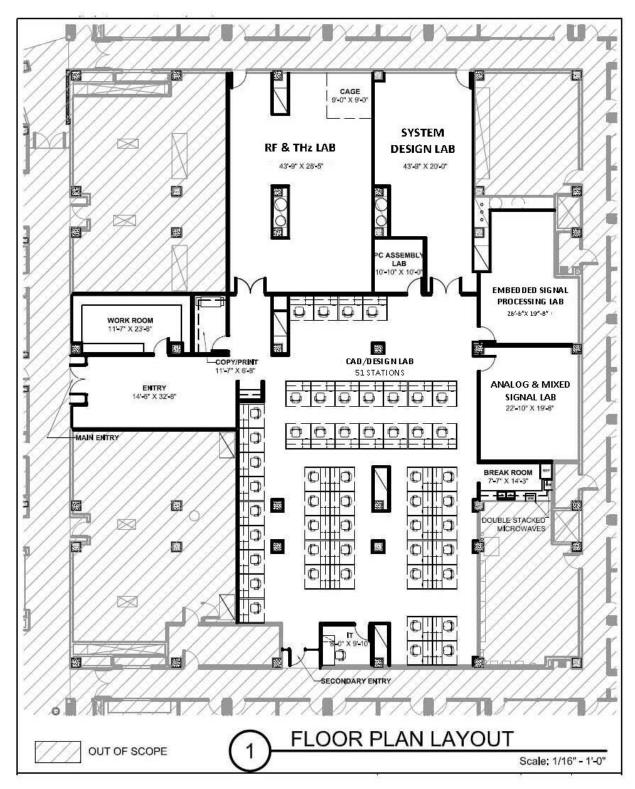

**Figure 7** is a 3D sketch of the facility, which was completed in August 2010, and is currently being brought online. The facility includes RF and THz, Integrated System Design, Embedded Signal Processing, and Analog & Mixed Signal laboratories as well as a CAD/Design laboratory structured to promote collaborative research. **Figure 7** presents the facility floor plan showing the dimensions of each laboratory.

#### Figure 7: TxACE research facility

The close proximity of researchers in an open layout enables natural interaction and compels sharing of knowledge and instrumentation among the students and faculty. The TxACE analog research facility is one of the best equipped university-based electronics laboratories in the state, and the RF and THz laboratory will be one of the best in the nation.

Figure 8: TxACE research facility floor plan

#### **RESEARCH PROJECTS AND INVESTIGATORS**

During 2009-2010 TxACE grew to be the largest analog technology center in the world on the basis of funding and the number of principal investigators. **Table 1** lists the names of the 68 principal investigators from 26 academic institutions with directed research tasks funded by TxACE. Seven schools (Rice, SMU, Texas A&M, Texas Tech, University of North Texas, UT Austin, UT Dallas) are in Texas. Nineteen are outside Texas. Three (Seoul National University, Cambridge University, National University of Ireland, Maynooth) are outside the U.S. Of the 68 investigators, 35 are from Texas. The center supports 73 graduate students and during the past year nine PhD and three MS degrees were awarded to TxACE students.

| Investigator            | Institution     | Investigator           | Institution     | Investigator            | Institution                      |

|-------------------------|-----------------|------------------------|-----------------|-------------------------|----------------------------------|

| David Allstot           | U Washington    | Mona Hella             | Rennselaer      | Un-Ku Moon              | Oregon State                     |

| Bertan Bakkaloglu       | Arizona State   | Rashaunda Henderson    | UT Dallas       | Tamal Mukherjee         | Carnegie Mellon                  |

| Poras Balsara           | UT Dallas       | Sebastian Hoyos        | Texas A&M       | Won Namgoong            | UT Dallas                        |

| Bhaskar Banerjee        | UT Dallas       | Roozbeh Jafari         | UT Dallas       | Ken O                   | UT Dallas                        |

| Leonidas Bleris         | UT Dallas       | Aydin Ilker Karsilayan | Texas A&M       | Vojin Oklobdzija        | UT Dallas                        |

| Andrew Blanchard        | UT Dallas       | Sayfe Kiaei            | Arizona State   | Sule Ozev               | Arizona State                    |

| Shawn Blanton           | Carnegie Mellon | Jaeha Kim              | Seoul Nat'l U   | Sam Palermo             | Texas A&M                        |

| Joe Brewer              | U Florida       | Elias Kougianos        | U North Texas   | Larry Pileggi           | Carnegie Mellon                  |

| Choong-Yul Cha          | UT Dallas       | Farinaz Koushanfar     | Rice            | John Ringwood           | NUI Maynooth                     |

| Abhijit Chatterjee      | Georgia Tech    | Hoi Lee                | UT Dallas       | Elyse Rosenbaum         | U Illinois, Urbana-<br>Champaign |

| Degang Chen             | Iowa State      | Changzhi Li            | Texas Tech      | Jaijeet<br>Roychowdhury | UC Berkeley                      |

| Frank De Lucia          | Ohio State      | Donald Yu-Chun Lie     | Texas Tech      | Rob Rutenbar            | Carnegie Mellon                  |

| William Eisenstadt      | U Florida       | Peng Li                | Texas A&M       | Mohammad<br>Saquib      | UT Dallas                        |

| Kamran Entesari         | Texas A&M       | Xin Li                 | Carnegie Mellon | Carl Sechen             | UT Dallas                        |

| Brian L. Evans          | UT Austin       | Jin Liu                | UT Dallas       | Naresh Shanbhag         | U Illinois, Urbana-<br>Champaign |

| Terri Fiez              | Oregon State    | Dongsheng Ma           | U Arizona       | Michael Shur            | Rennselaer                       |

| Randy Geiger            | Iowa State      | H.A. Mantooth          | U Arkansas      | Jose Silva-<br>Martinez | Texas A&M                        |

| Ranjit Gharpurey        | UT Austin       | Yiorgos Makris         | Yale            | V. Stojanovic           | MIT                              |

| Ping Gui                | SMU             | Jose Silva-Martinez    | Texas A&M       | Murat Torlak            | UT Dallas                        |

| Pavan Kumar<br>Hanumolu | Oregon State    | Kartikeya Mayaram      | Oregon State    | Eric Vogel              | UT Dallas                        |

| Ramesh Harjani          | U Minnesota     | Richard McMahon        | Cambridge       | Xi-Cheng Zhang          | Rennselaer                       |

| Arjang Hassibi          | UT Austin       | Kathleen Melde         | U Arizona       | Dian Zhou               | UT Dallas                        |

| Robert Heath            | UT Austin       | Saraju Mohanty         | U North Texas   |                         |                                  |

#### Table 1: Principal and co-principal investigators of TxACE during reporting period

#### SUMMARIES OF RESEARCH PROJECTS, ACCOMPLISHMENTS AND PUBLICATIONS

The 66 research projects funded through TxACE during 2009-2010 are listed in **Table 2** below by Semiconductor Research Corp. task identification number. Despite being in existence for only two years, TxACE is making significant research progress. **Table 3** lists the major research accomplishments for the center from Sept. 1, 2009, to Aug. 31, 2010, while **Table 4** summarizes the number of publications and inventions resulting from TxACE research during the period. Following the tabulations, brief summaries of each project are provided.

| #  | Task     | Task Title                                                                                                                      | PI                       | Institution                        |

|----|----------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------|

| 1  | 1836.002 | Adaptive High Dynamic Range Equalizer and Automatic Skew Compensation for High-Speed Data Communications                        | Liu, Jin                 | UT Dallas                          |

| 2  | 1836.003 | Temperature Compensated, High Common Mode Range, Cu-Trace Based<br>Current Shunt Monitors                                       | Bakkaloglu,<br>Bertan    | Arizona State                      |

| 3  | 1836.004 | Robust Design of Low Power Small Area Data Converters in Low Voltage<br>Digital Processes                                       | Geiger, Randall          | Iowa State                         |

| 4  | 1836.005 | Design and Implementation of a Large-N Low-Jitter Digitally-Controlled<br>Oscillator (DCO)-based Frequency Multiplier           | Gui, Ping                | SMU                                |

| 5  | 1836.006 | Multi-Core and Distributed Parallel Simulation for Design and Verification of Custom Digital and Analog ICs                     | Li, Peng                 | Texas A&M                          |

| 6  | 1836.007 | Novel Instruction Set Architecture Designs for Programmable Multiple<br>Standard Radio Processors                               | Oklobdzija, Vojin        | UT Dallas                          |

| 7  | 1836.008 | Digital Assisted Millimeter-Wave CMOS Circuits                                                                                  | O, Kenneth               | UT Dallas                          |

| 8  | 1836.011 | Power Minimization and Yield Optimization in Digital IC's                                                                       | Sechen, Carl             | UT Dallas                          |

| 9  | 1836.012 | Structural Fault Modeling, Testing, and Defect Level Estimation for Analog/RF Circuits                                          | Ozev, Sule               | Arizona State                      |

| 10 | 1836.013 | Wideband Receiver Architectures in Digital Deep Submicron CMOS                                                                  | Hoyos,<br>Sebastian      | Texas A&M                          |

| 11 | 1836.014 | Digital Phase-Locking Circuits for Clock Generation and Data Recovery in<br>High-Speed Frequency Multiplier Communication Links | Hanumolu,<br>Pavan Kumar | Oregon State                       |

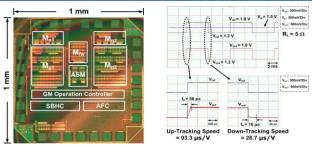

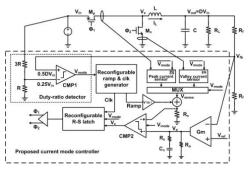

| 12 | 1836.015 | Software-Defined Digital Multiple-Output DC-DC Converter for Dynamic Thermal Management                                         | Ma, Brian                | UT Dallas                          |

| 13 | 1836.016 | Bridging the Synthesis Gap from Circuits to Systems for Scaled Mixed-Signal Silicon                                             | Mukherjee,<br>Tamal      | Carnegie<br>Mellon                 |

| 14 | 1836.017 | Performance-Oriented DVS-Compatible Single-Inductor Multiple-Output<br>Power Converters                                         | Ma, Brian                | UT Dallas                          |

| 15 | 1836.018 | Transistor Sizing and Voltage Scaling for Minimal Energy at Fixed Performance                                                   | Oklobdzija, Vojin        | UT Dallas                          |

| 16 | 1836.019 | Digitally-Enhanced Energy-Efficient High-Speed I/O Links                                                                        | Shanbhag,<br>Naresh      | U Illinois<br>Urbana-<br>Champaign |

| 17 | 1836.020 | Low-Complexity High-Performance Analog-to-Digital Converters in Submicron CMOS                                                  | Moon, Un-Ku              | Oregon State                       |

| 18 | 1836.021 | CAD Algorithms and Tools for Fast and Accurate PLL Design in the Presence of Variability                                        | Roychowdhury,<br>Jaijeet | UC Berkeley                        |

| 19 | 1836.022 | High-Speed MIMO Signaling Techniques for Single-Ended Parallel I/O                                                              | Harjani, Ramesh          | U Minnesota                        |

#### Table 2: Funded research projects at TxACE by SRC task identification number

| #  | Task     | Task Title                                                                                                                     | PI                       | Institution        |

|----|----------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|

| 20 | 1836.023 | Fast Algorithms for SPICE-Level Simulation of Large Structured Circuits                                                        | Roychowdhury,<br>Jaijeet | UC Berkeley        |

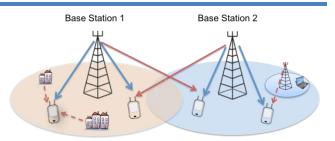

| 21 | 1836.024 | MIMO at the Cell Edge for High Bandwidth Communication in Interference<br>Limited Cellular Systems                             | Heath, Robert            | UT Austin          |

| 22 | 1836.025 | Ultra Low Power ADCs for Wireless Communications                                                                               | Fiez, Terri              | Oregon State       |

| 23 | 1836.026 | Automatic RF Impedance Correction Circuits for SoC RF/Mixed-Signal ATE Test                                                    | Eisenstadt,<br>William R | U Florida          |

| 24 | 1836.027 | Automatic RF Impedance Correction Circuits for SoC RF/Mixed-Signal ATE Test                                                    | Melde,<br>Kathleen       | U Arizona          |

| 25 | 1836.028 | Tools and Algorithms for Behavioral Model Generation of Analog/Mixed-<br>Signal Circuits                                       | Mantooth,<br>Homer Alan  | U Arkansas         |

| 26 | 1836.029 | Statistical Analysis of Parametric Measurements and its Applications in Analog/RF Test                                         | Makris, Yiorgos          | Yale               |

| 27 | 1836.030 | Fast PVT-Tolerant Physical Design of RF IC Components                                                                          | Mohanty,<br>Saraju       | UNT                |

| 28 | 1836.031 | Variation Tolerant Analog Design based on Generalized<br>Kharitonov/Lyapunov Theory                                            | Zhou, Dian               | UT Dallas          |

| 29 | 1836.032 | Millimeter Wave Phase-Locked Loop Design with Enhanced Tolerance to<br>Process and Temperature Variation                       | Gharpurey,<br>Ranjit     | UT Austin          |

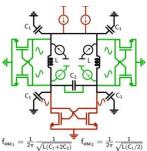

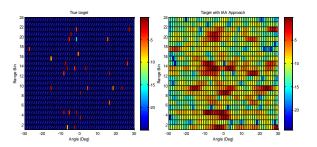

| 30 | 1836.033 | MIMO Radar for Pixel Reduction in mm-Wave Imaging                                                                              | Saquib,<br>Mohammad      | UT Dallas          |

| 31 | 1836.034 | 77-81 GHz CMOS Transceiver with Built-In Self Test and Healing                                                                 | Banerjee,<br>Bhaskar     | UT Dallas          |

| 32 | 1836.035 | Development of CMOS Sub-Terahertz Receivers for Spectrometers                                                                  | Banerjee,<br>Bhaskar     | UT Dallas          |

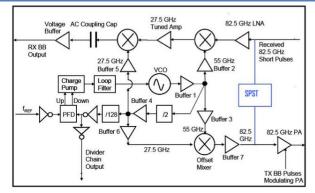

| 33 | 1836.036 | Signal Generation for 200-300 GHz Spectrometer                                                                                 | O, Kenneth               | UT Dallas          |

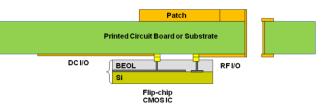

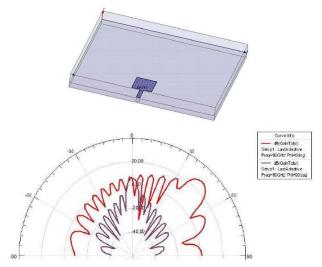

| 34 | 1836.037 | Development of Antenna and Chip Interface Systems for Millimeter Wave and Sub-Millimeter Wave Applications                     | Henderson,<br>Rashaunda  | UT Dallas          |

| 35 | 1836.038 | A Hybrid 14-bit Analog-to-Digital Converter for Broadband Applications                                                         | Silva-Martinez,<br>Jose  | Texas A&M          |

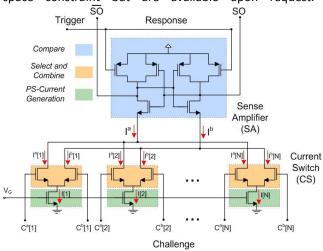

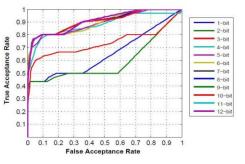

| 36 | 1836.039 | UxIDs: Unclonable Mixed-Signal Integrated Circuits Identification                                                              | Koushanfar,<br>Farinaz   | Rice               |

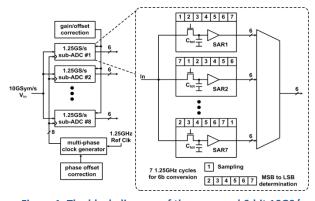

| 37 | 1836.040 | Energy-Efficient CMOS 10GS/s 6-bit ADC with Embedded Equalization                                                              | Palermo, Sam             | Texas A&M          |

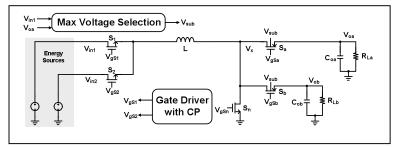

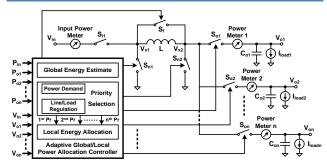

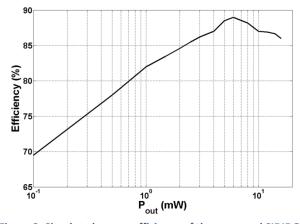

| 38 | 1836.041 | A High-Efficiency Single-Inductor Multiple-Input Multiple-Output Integrated DC/DC Converter for Energy-Harvesting Applications | Lee, Hoi                 | UT Dallas          |

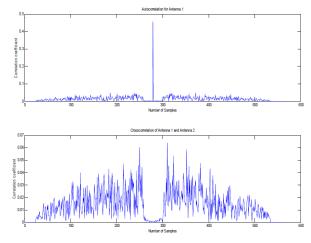

| 39 | 1836.042 | Adaptive Data Prediction Based Receiver for Power-Efficient High-Resolution Ultrasound Imaging Systems                         | Ma, Brian                | UT Dallas          |

| 40 | 1836.043 | High-Voltage Amplifier Technology                                                                                              | Gui, Ping                | SMU                |

| 41 | 1836.044 | Statistical Models and Methods for Design and Test of Non-Digital Components                                                   | Li, Xin                  | Carnegie<br>Mellon |

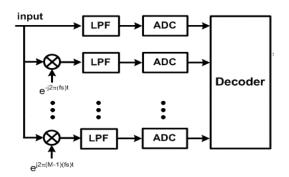

| 42 | 1836.045 | Frequency Channelized ADC for Wide Bandwidth Systems                                                                           | Namgoong,<br>Won         | UT Dallas          |

| 43 | 1836.046 | Reconfigurable Antenna Interface for Low-Power Wireless Sensor Nodes                                                           | Allstot, David           | U Washington       |

| 44 | 1836.047 | Integration of Millimeter Wave Antennas Using System in Package Techniques                                                     | Henderson,<br>Rashaunda  | UT Dallas          |

| 45 | 1836.048 | Millimeter and Submillimeter Gas Sensors: System Architectures for CMOS Devices                                                | De Lucia, Frank          | Ohio State         |

| 46 | 1836.049 | On-Chip Current-Sensing Techniques for Switching DC/DC Converters                                                              | Lee, Hoi                 | UT Dallas          |

#### Table 2: continued

#### Table 2: continued

| #  | Task     | Task Title                                                                                                                                        | PI                          | Institution   |

|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|

| 47 | 1836.050 | Feed-Forward Multi-Phase Clock Generation                                                                                                         | Liu, Jin                    | UT Dallas     |

| 48 | 1836.052 | An Ultra-low Power Signal Processing with Smart Analog-enabled<br>Pre-Conditioning Stage for Inertial Sensing Applications                        | Jafari, R.&<br>Namgoong, W. | UT Dallas     |

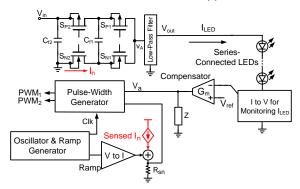

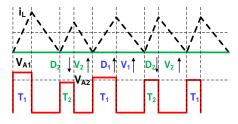

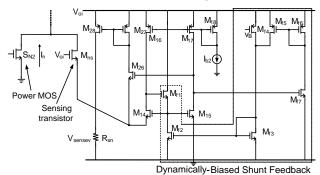

| 49 | 1836.053 | High-Efficiency Highly-Integrated LED Driver Systems for Solid-<br>State Lighting Applications                                                    | Lee, Hoi & Zhou,<br>Dian    | UT Dallas     |

| 50 | 1836.054 | Silicon Based Beamforming Arrays for Millimeter Wave Systems                                                                                      | Torlak, Murat               | UT Dallas     |

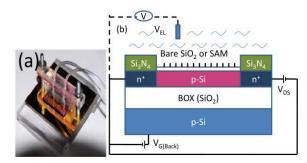

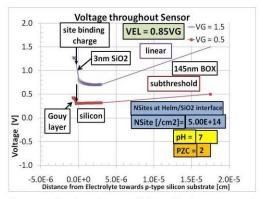

| 51 | 1836.055 | SPICE Models and Analog Circuits for Nanoscale Silicon Chemical-<br>and Biological-Sensors                                                        | Vogel, Eric                 | UT Dallas     |

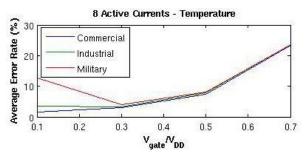

| 52 | 1836.057 | High Accuracy All-CMOS Temperature Sensor with Low-Voltage<br>Low-Power Subthreshold MOSFETs Front-End and Performance-<br>Enhancement Techniques | Li, Changzhi                | Texas Tech    |

| 53 | 1836.058 | Hierarchical Model Checking for practical Analog/Mixed-Signal<br>Design Verification                                                              | Li, Peng &<br>Liu, Jin      | Texas A&M     |

| 54 | 1836.060 | Design Techniques for Scalable, Sub-1mW/Gbps Serial I/O<br>Transceivers                                                                           | Palermo, Sam                | Texas A&M     |

| 55 | 1836.061 | Analog Computing in Human Cells                                                                                                                   | Bleris, Leonidas            | UT Dallas     |

| 56 | 1836.062 | System-Level Models and Design of Power Delivery networks with<br>On-Chip Voltage Regulators                                                      | Li, Peng                    | Texas A&M     |

| 57 | 1836.063 | Power line Communications for Enabling Smart Grid Applications                                                                                    | Evans, Brian L.             | UT Austin     |

| 58 | 1836.064 | Ultra-Low-Power Analog Front-End IC Design for Implantable<br>Cardioverter Defibrillator                                                          | Lie, Donald Yu-Chun         | Texas Tech    |

| 59 | 1836.065 | Energy Efficient Comparator Elements for A/D Converters and High-Speed I/Os                                                                       | Oklobdzija, Vojin           | UT Dallas     |

| 60 | 1836.066 | A Fully-Integrated CMOS Platform for Microwave-Based Label-<br>Free DNA Sensing                                                                   | Entesari, Kamran            | Texas A&M     |

| 61 | 1836.067 | Characterization of CMOS Basic Building Blocks for Sub-THz<br>Wideband Transmitters                                                               | Hella, Mona                 | Rensselaer    |

| 62 | 1836.068 | Global Convergence Analysis of Mixed-Signal Systems                                                                                               | Kim, Jaeha                  | Seoul Nat'l U |

| 63 | 1836.069 | Electronic Systems for Small-Scale Wind Turbines                                                                                                  | McMahon, Richard            | Cambridge     |

| 64 | 1836.070 | Optimum Control of Power converters                                                                                                               | Ringwood, John              | NUI Maynooth  |

| 65 | 1836.071 | Design of Photovoltaic (PV) Power Harvesting CMOS Ics                                                                                             | Hassibi, Arjang             | UT Austin     |

| 66 | 1836.072 | Low Cost Test of High Speed Signals                                                                                                               | Chatterjee, Abhijit         | GA Tech       |

#### Table 3: TxACE Research Accomplishments September 2009 through August 2010

| Category | Accomplishment                                                                                                                                                                                                                                                                                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuits | Demonstrated a tunable 60-GHz tuned amplifier using variable inductors in 45-nm<br>CMOS. (1836.008-1836.10, PIs: K. O, University of Texas, Dallas, J. Brewer, University<br>of Florida                                                                                                                                                                       |

| Circuits | Demonstrated a tool that lowers dynamic power of digital integrated circuits by<br>more than 35% and lowers leakage power by more than 70%, compared to that<br>generated using state-of-the-art EDA tools. (1836.011, PI: C. Sechen, University of<br>Texas, Dallas)                                                                                         |

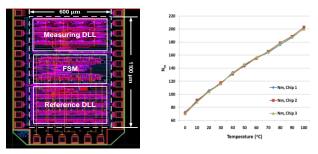

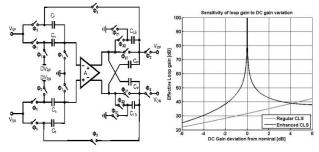

| Circuits | Demonstrated a supply-regulated PLL architecture that eliminates the tradeoff<br>between supply noise rejection and oscillator phase noise suppression. The PLL is<br>the first to employ bandwidth tracking and achieves the highest supply noise<br>immunity, best power efficiency and low jitter. (1836.014, PI: P. Hanumolu, Oregon<br>State University) |

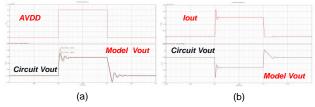

| Circuits | Demonstrated a DC-DC power conversion system with software-defined control<br>schemes. The system utilizes an all-digital temperature sensor with high resolution<br>and low static power consumption. (1836.015, PI: D. Ma, University of Texas, Dallas<br>(Formerly of University of Arizona)                                                               |

| Circuits | Demonstrated a digital SIMO step-up/down power converter for DVS-enabled<br>multicore systems. An adaptive freewheel switching control mechanism is<br>demonstrated for cross regulation suppression. (1836.017, PI: D. Ma, University of<br>Texas, Dallas (Formerly of University of Arizona))                                                               |

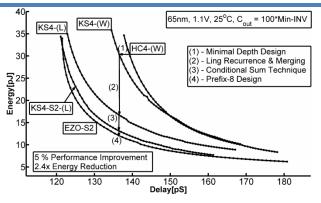

| Circuits | By exploring energy-delay trade-offs in algorithm, recurrence, wiring, and circuit topology, developed the most energy efficient 64-bit adder (EZO-S2). (1836.018, PI: P. V. Oklobdjiza, University of Texas, Dallas)                                                                                                                                         |

| Circuits | Developed a BER-aware 3-b ADC architecture with shaping gain > 30dB that has 10 <sup>6</sup> X lower BER than a conventional 4-b ADC, and 50% savings in power consumption for flash converters. (1836.019, PIs: N. Shanbhag and E. Rosenbaum, University of Illinois, Urbana Champaign)                                                                      |

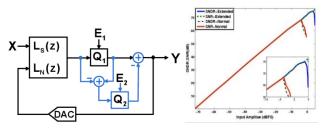

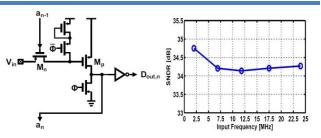

| Circuits | Demonstrated a $\Delta\Sigma$ ADC that uses an auxiliary quantizer to significantly raise the maximum input stable range. Demonstrated a low complexity synthesizable all-digital domino logic based ADC. (1836.020, PI: U. Moon, Oregon State University)                                                                                                    |

| Circuits | Developed a MIMO architecture for reducing far end cross talk with reduced power<br>and area. Achieved reliable signal integrity with narrow channel spacing, increasing<br>data throughput. (1836.022, PI: R. Harjani, University of Minnesota)                                                                                                              |

#### Table 3: Continued

| Category      | Accomplishment                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuits      | Showed uncoordinated interference in MIMO communication proposed for the latest cellular standard causes the goodput gain to decay doubly exponentially with feedback delay. Proposed rate backoff at the transmitter maximizes the achievable ergodic goodput. (1836.024, PI: R. Heath, University of Texas, Austin)                                                               |

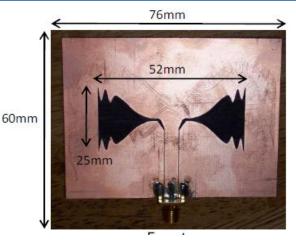

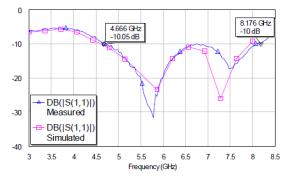

| Circuits      | A broadband planar bowtie antenna with 55% bandwidth has been achieved.<br>(1836.037, PIs: R. Henderson, A. Blanchard, University of Texas, Dallas)                                                                                                                                                                                                                                 |

| Circuits      | A single inductor dual-input dual-output (SIDIDO) boost converter is developed for<br>energy harvesting applications. A switching-time-aware pulse-frequency modulation<br>control scheme is proposed to enable the converter to achieve the peak power<br>efficiency of 89% over the load current range from 0.1mW to 16mW. (1836.041, PI:<br>H. Lee, University of Texas, Dallas) |

| Circuits      | Demonstrated an adaptive data prediction based ultrasound receiver with ~27-30 dB higher output dynamic range while using a lower resolution ADC (10 bit instead of 12bit). (1836.042 D. Ma, University of Texas, Dallas (Formerly of University of Arizona))                                                                                                                       |

| Circuits      | Using current mode control in a buck regulator, reduced (2-5 x) off-chip inductor size to 1 mH and reduced chip size by ~5 to 10X. The regulator incorporates dynamically-biased shunt feedback in both peak and valley current sensors for improving the sensing speed to 2.5MHz. (1836.049, PI: H. Lee, University of Texas, Dallas)                                              |

| Circuits      | Created equivalent circuit model and understood impact of back-gate bias on silicon<br>on insulator based nanowire sensor operation. (1836.055, PI: E. Vogel, University of<br>Texas, Dallas)                                                                                                                                                                                       |

| CAD &<br>Test | Developed multi-algorithm parallel circuit simulation techniques using 8 threads<br>that speed up run time by more than 10X over serial single algorithms. (1836.006,<br>PI: Peng Li, Texas A&M)                                                                                                                                                                                    |

| CAD &<br>Test | Developed variability-enabled nonlinear phase models for PLLs that enable accurate simulation of PLL dynamics orders of magnitude faster than comparable alternatives. (1836.021, PI: J. Roychowdhury, University of California, Berkeley)                                                                                                                                          |

#### Table 3: Continued

| Category      | Accomplishment                                                                                                                                                                                                                                                                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAD &<br>Test | Developed the hierarchical Differential Algebraic Equation (HDAE) formulation core<br>for enabling multilevel algorithms that reduces memory usage and speeds up<br>simulation. The HDAE core has been used to enable multilevel DC, AC, transient and<br>harmonic balance analyses. (1836.023, PI: J. Roychowdhury, University of California,<br>Berkeley)               |

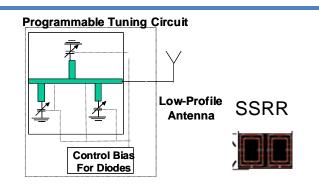

| CAD &<br>Test | Demonstrated a new automatic match circuit tuner using square split ring resonators (SSRR) that is 2.5x smaller in size. (1836.026, PI: K. Melde, University of Arizona)                                                                                                                                                                                                  |

| CAD &<br>Test | Showed that by employing the NSGA-II genetic algorithm as a heuristic basis for feature selection, latent correlations between kerf/inline parameters and module final test parameters can be uncovered. (1836.029, PI: Y. Makris, Yale University)                                                                                                                       |

| CAD &<br>Test | Developed a unified statistical analysis engine for SRAM performance, yield,<br>reliability and testability that uses a novel Gibbs sampling algorithm to improve the<br>accuracy and speed of analysis. Demonstrated 3~10x runtime speedup over other<br>state-of-the-art CAD techniques without any accuracy loss. (1836.044, PI: X. Li,<br>Carnegie Mellon University) |

Table 4: TxACE number of publications during the reporting period

| Conference<br>Papers | Journal Papers | Invention<br>Disclosures |

|----------------------|----------------|--------------------------|

| 62                   | 13             | 2                        |

### TASK ID# 1836.003: TEMP. COMPENSATED, HIGH COMMON MODE RANGE, CU-TRACE BASED CURRENT SHUNT MONITOR AMPLIFIER

BERTAN BAKKALOGLU, ARIZONA STATE UNIVERSITY, <u>bertan.bakkaloglu@asu.edu</u> SAYFE KIAEI, ARIZONA STATE UNIVERSITY

#### SIGNIFICANCE AND OBJECTIVES

A current shunt monitor that accurately amplifies 10mV range voltages across a sense resistor, in the presence of large common-mode voltage up to 26V is presented. The design was completed and fabricated in 0.7um CMOS process with less than 10uV of input offset and 1uV/ $\sqrt[2]{Hz}$  of flicker noise. CMRR over 120dB is also achieved.

#### TECHNICAL APPROACH

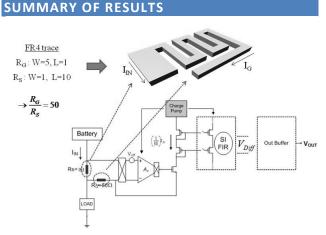

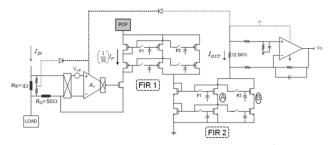

Instead of using external sensing resistor in the current path, existing PCB Cu-trace is used as sensing resistors for cost reduction by eliminating high accuracy external components. Better internal resistive matching and equal resistance variation over all the process corners and temperatures achieved by designing Input sensing (R<sub>s</sub>) and gain (R<sub>G</sub>) resistors in ratio,  $\frac{R_G}{R_S} = 50$ . A switching current mode FIR filter is used to cancel chopping ripple in current domain instead of using conventional voltage mode ripple reduction techniques.

Figure 1: Matched input resistors on an FR4 trace.

The patterning of proposed Cu-Trace resistors is shown in Figure 1. Input chopping technique is applied to fulfill less than 10uV of input referred offset requirement. Since chopping technique causes ripple due to the switching, there needs to be a function that can suppress down the ripple at chopping frequency harmonics. A switching current mode FIR filter which samples and averages the two different phase chopped input signals while reducing the chopping ripples with its first order hold sinc<sup>2</sup> function is implemented. The switching current mode (SI) FIR filter not only reduce down the ripple by its second order notching mechanism, but also recovers original offset-free DC input current by averaging the offset-containing input signals. The following first order hold sinc<sup>2</sup> function as in eq. (1) is realized in the circuit in Figure 2.

$$\left|\frac{1-e^{-sT}}{s}\right|^2 = T \frac{\left|\sin\left(\frac{wT}{2}\right)\right|^2}{\left|\frac{wT}{2}\right|^2} = T \operatorname{sinc}^2\left(\frac{wT}{2}\right) \tag{1}$$

Figure 2: Detailed diagram of first order hold sinc<sup>2</sup> FIR.

Overall, the presented instrumentation amplifier has clear rail to rail operation with less than 10uV input referred offset and CMRR of 120 dB. The device has been fabricated with 0.7 um AMIS (ON Semiconductor) I2T100 process.

| Table | 1: | specifications | of | the | design |

|-------|----|----------------|----|-----|--------|

|-------|----|----------------|----|-----|--------|

| Input voltage | Offset | CMRR | Input noise     |

|---------------|--------|------|-----------------|

| (V)           | (uV)   | (dB) | $(V/\sqrt{Hz})$ |

| 0~26          | 10     | 120  | 1u              |

**Keywords:** Chopper stabilizers, flicker noise, Instrumentation amplifier, CMRR, ripple/residue reduction

#### INDUSTRY INTERACTIONS

Texas Instruments Tucson HPA (High Performance Analog) and Freescale Inc. Tempe, AZ work closely with ASU scientists

#### MAJOR PAPERS/PATENTS

H.S. Yeom, B. Bakkaloglu, "High Common Mode Range, Cu-Trace Based Current Shunt Monitor Amplifier," (Invited) SRC 2010 TECHCON, September, 2010, Austin, Texas.

### TASK ID# 1836.004, ROBUST DESIGN OF LOW POWER SMALL AREA DATA CONVERTERS IN LOW VOLTAGE DIGITAL PROCESSES

RANDALL GEIGER, IOWA STATE UNIVERSITY, <u>rlgeiger@iastate.edu</u> DEGANG CHEN, IOWA STATE UNIVERSITY, <u>djchen@iastate.edu</u>

#### SIGNIFICANCE AND OBJECTIVES

The objective is to develop a method for practical onchip testing of ADCs (BIST) and to use test results to enhance ADC performance through BIST-based calibration. This offers potential for reducing die area and power while enhancing parametric performance and reliability of systems that employ embedded data converters.

#### **TECHNICAL APPROACH**

Initially methods of testing ADCs will be developed that do not require precision test equipment but that provide reliable parametric test performance. Emphasis will be where placed on approaches excitation and measurement circuitry can be placed on-chip with minimal area overhead. Preliminary results for linearity testing have been obtained but for a practical BIST approach, all critical parametric parameters of an ADC must be testable. In this work emphasis is placed both upon reducing the size of the test circuitry and on extending previous results to include other parametric parameters such as spectral performance, gain, and offset parameters.

#### SUMMARY OF RESULTS

A comparison of several different algorithms that can provide INL and DNL test results without requiring precise or known signal generators has been made. This comparison has been restricted to testing strategies based upon the Functionally Related Excitation (FRE) method of on-chip testing. This comparison shows that there are not significant differences in parametric performance between the different test approaches that have been published but some offer reductions in hardware complexity.

Methods of generating the test signals have been investigated. Emphasis has been placed upon circuits that can generate a sufficiently constant shift and on methods for using a series of faster-rising ramps that do not have correlation of break points from one ramp signal to the next. Results show that simple shift generators that exploit the offset voltage in an operational amplifier that results from a switchable asymmetry are adequate for INL testing of ADCs with resolution up to 18 bits. The concept is illustrated in the following figure where the mismatch in bias current of

Keywords: BIST, Analog-BIST, SEIR, Self-calibration

#### **STUDENTS**

Jingbo Duan, Bharath Vasan, and Siva Sudani

#### INDUSTRY INTERACTIONS

Texas Instruments, Liaisons: Irene Deng, Steve Howard

#### MAJOR PAPERS/PATENTS

[1] Duan J. et al., "Cost Effective Signal Generators for ADC BIST", ISCAS, 2009.

[2] Duan J. et al., "Stimulus Generator for SEIR Method Based ADC BIST", NAECON 2009.

[3] Vasan, B. et al, "Signal generators for cost effective BIST of ADCs", ECCTD 2009.

[4] Duan, J. "Chip Implementation of Low Overhead ADC BIST", TECHON 2009.

[5] Duan, J. et al., "Phase Control of Triangular Stimulus for ADC BIST", ISCAS, 2010.

[6] Duan, J. et .al., "INL Based Spectral Performance Estimation for ADC BIST", ISCAS 2010.

[7] Vasan, B. et al. ,"Linearity testing of ADCs using low linearity stimulus and Kalman filtering", ISCAS 2010.

[8] Duan, J. et al., "A New Method for Estimating Spectral Performance of ADC from INL", ITC 2010 (to appear).

[9] Vasan, et al "Linearity testing of ADCs using imprecise sinusoidal excitations", NAECON 2010.

[10] Duan, J. et al., "Sensorless Temperature Measurement Based on ADC Input Noise Measurement", NAECON 2010.

[11] Duan, J., "Phase Control of Triangular Stimulus for ADC BIST", TECHON 2010.

### TASK ID# 1836.005, A LARGE-N LOW-JITTER DIGITALLY-CONTROLLED OSCILLATOR (DCO)-BASED FREQUENCY MULTIPLIER

PING GUI, SOUTHERN METHODIST UNIVERSITY, pgui@smu.edu

#### SIGNIFICANCE AND OBJECTIVES

Conventional PLL-based frequency multiplier becomes not feasible when the multiplication ratio N is very large (N  $\geq 1000$ ). This project seeks to design a digital frequency multiplier that is able to handle such a large N with very low jitter. This approach employs minimum analog complexity, and is easily transferable across technologies.

#### **TECHNICAL APPROACH**

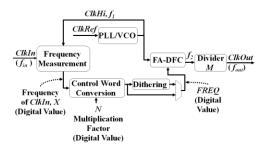

The proposed frequency multiplier utilizes a Flying-Adder-based Digital Controlled Oscillator (FA-DCO) and a frequency-to-digital converter (FDC) in a unique configuration. By employing both an FDC and a DFC, frequencies are represented in the digital or software domain. Digital or software processing can be utilized to produce the desired relationship  $f_{out} = N \cdot f_{in}$ , where the multiplication ratio N can be either an integer or a real number. This frequency multiplier is capable of generating a large range of frequencies instantaneously. Additionally, a digital modulation technique is introduced and implemented in this architecture to reshape the clock spectrum for electromagnetic interference (EMI) reduction.

#### SUMMARY OF RESULTS

We have designed and implemented the FA-DFC-based frequency synthesizer structure (show in Fig. 1) capable of generating a low-jitter high-frequency output clock from a noisy low-frequency input and providing a range of available frequencies [1]. Silicon measurement results have demonstrated the following features of this frequency multiplier: 1) the input clock frequency can be very low, even in Hz range, and the multiplication ratio N can be very large (N  $\ge$  1000); 2) the jitter associated with the input will not propagate to the output; 3) the output clock can follow instantly with the change in input clock frequency or the multiplication ratio; 4) digital modulation circuits are shown capable of spreading the clock spectrum or reducing the spurious frequencies. In addition, we have also completed a thorough mathematical analysis on the effects of the FA-based clock on embedded systems such as DACs [2-3]. A Signed-Binary-Addition-Based Redundant Digital-to-Frequency converter is also proposed and implemented to eliminate the speed bottleneck of the FA-DCO [4]. Moreover, a new DCO architecture which employs both

sigma-delta Fractional-N and the Flying-Adder synthesizer is proposed and implemented to improve the jitter performance of the FA-DCO [5].

Figure 1: The block diagram of the FA-DFC-based frequency generator capable of handling large multiplication ratio N.

**Keywords:** Frequency Multiplier, Fractional-N, Flying-Adder, Jitter, Spread Spectrum, Sigma Delta

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### **MAJOR PAPERS/PATENTS**

[1] W. Chen, P. Gui and L. Xiu, "A Low-Jitter Large-N Frequency Multiplier", SRC TECHCON, 2008.

[2] P. Gui, Z. Gao, C. W. Huang, L. Xiu, "The Effects of Flying-Adder Clocks on Digital-to-Analog Converters", *IEEE Transaction on Circuits and Systems II* in Vol. 57, No. 1, pp.1-5, 2010.

[3] L. Xiu, C. W. Huang, P. Gui, "The Analysis of Harmonic Energy Distribution Portfolio For Digital-to-Frequency Converter", To appear in *IEEE Transactions on Instrumentation and Measurement*, Vol. 59, No. 4, 2010.

[4] W. Chen, M.A. Thornton, and P. Gui, "A Redundant Signed Binary Addition Based Digital-to-Frequency Converter", *IEE Electronics Letters*, vol. 45, no. 2, pp. 824-826, July 2009.

[5] C-W Huang, P. Gui, "A 250 MHz-4 GHz Sigma-Delta Fractional-N Frequency Synthesizer with Adjustable Duty Cycle", Proceedings of *International Symposium on Circuits and System (ISCAS)*, 2010.

## TASK ID# 1836.006, MULTI-CORE & DISTRIBUTED PARALLEL SIMULATION FOR DESIGN AND VERIFICATION OF CUSTOM DIGITAL AND ANALOG ICS

PENG LI, TEXAS A&M UNIVERSITY, pli@tamu.edu

#### SIGNIFICANCE AND OBJECTIVES

Transistor-level circuit simulation is a fundamental, yet computationally intensive, design and verification enabler for wide ranges of digital and analog circuits. We address the significant simulation challenge by developing novel parallel simulation paradigms on multicore and distributed computing platforms.

#### **TECHNICAL APPROACH**

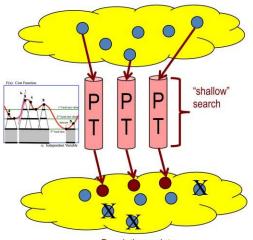

Novel parallel computing paradigms are developed to exploit rich simulation application level parallelisms. These approaches are designed to minimize interprocessor communication overhead, achieve good scalability, and simplify parallel programming implementation. We not only develop intra-algorithm but also unconventional inter-algorithm parallel approaches. In the latter, multiple simulation algorithms are launched for a single simulation task. The goal is to create orthogonal opportunities such that massively parallel machines can be well utilized. Furthermore, we develop parallel performance models to facilitate static and runtime simulation code optimization.

#### SUMMARY OF RESULTS

We develop novel algorithms that complement conventional parallelization approaches and allow for efficient use of parallel hardware.

For harmonic balance based steady-state and envelope following analysis, we have developed a robust hierarchical preconditioner. It not only leads to fast convergence for strongly nonlinear problems but also is naturally parallelizable by construction. In the time domain, we have demonstrated a coarse-grained approach, Waveform Pipelining, for transient simulation. Transient responses at multiple time points are computed in parallel by exploiting multi-step numerical integration methods and predictive computing at future time points while guaranteeing the simulation convergence and accuracy. In a different perspective, by exploiting the recently developed telescopic numerical integration method, we have leveraged stable explicit numerical integration for parallel simulation. With a multi-level integration scheme, this approach addresses the known stability limitations of existing explicit methods and facilitates integration natural parallelization. The same basic principle has also been extended to a novel bi-directional parallel simulation approach for digital timing and steady-state analysis.

With an increased parallelization granularity, we have developed a multi-algorithm parallel circuit simulation (MAPS) framework. Unlike most existing approaches, MAPS exploits inter-algorithm parallelisms by launching multiple simulation algorithms in parallel for a given simulation task (Fig. 1 left). By properly synchronizing these algorithms on-the-fly, we exploit the diversity in simulation algorithms to achieve significant speedups over a standard serial single-algorithm reference, which employs backward Euler numerical integration and Newton iterative method (Fig. 1 right). The coarse grained nature of MAPS leads to simple parallel implementation and reuse of existing simulation codes.

| BE<br>Gear2<br>DASSL      | Circuit   | 4-thread<br>MAPS<br>speedup | 8-thread<br>HMAPS<br>speedup |

|---------------------------|-----------|-----------------------------|------------------------------|

| Simulation Algorithm Pool | Logic 1   | 7.39x                       | 9.98x                        |

| Alg1 Alg2 Alg3 ···        | Logic 2   | 13.0x                       | 23.12x                       |

|                           | Clock 1   | 10.60x                      | 6.29x                        |

| Core Core Cor             | Clock 2   | 19.36x                      | 37.89x                       |

| 1 2 ··· n                 | Clock 3   | 19.19x                      | 39.69x                       |

| global synchronizer ;     | LNA+Mixer | 7.22x                       | 7.16x                        |

Figure 1: left: multi-algorithm parallel circuit simulation; right: runtime speedups over a single-algorithm reference.

In the following year, we will develop parallel performance modeling approaches that allow for static and runtime optimization of MAPS.

**Keywords:** Circuit simulation, parallelization, transient analysis, steady-state analysis, parallel code optimization.

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, AMD, Freescale

#### MAJOR PAPERS/PATENTS

[1] X. Ye, W. Dong, P. Li and S. Nassif, IEEE/ACM ICCAD'09.

[2] W. Dong and P. Li, IEEE TCAD'09.

- [3] W. Dong and P. Li, IEEE/ACM ICCAD'09.

- [4] X. Ye and P. Li, IEEE/ACM DAC'10.

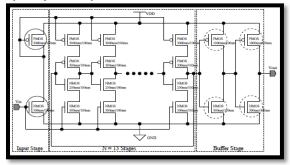

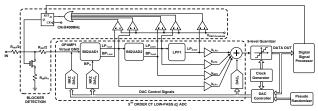

### TASK ID# 1836.007, SOFTWARE DEFINED/RECONFIGURABLE MULTI-MODE SERIAL LINK CONTROLLER ARCHITECTURE

VOJIN G. OKLOBDZIJA, UNIVERSITY OF TEXAS AT DALLAS, vojin@acsel-lab.com PORAS T. BALSARA, UNIVERSITY OF TEXAS AT DALLAS

#### SIGNIFICANCE AND OBJECTIVES

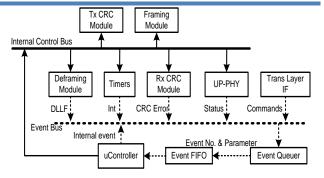

This work introduces a novel Multi-mode Serial Link Controller (MMSLC) for logic physical layer (PHY) and data link layer (DLL) of USB 3.0, PCIe 2.0 and SATA 3.0. This architecture may accommodate multiple revisions of existing protocols and also for standards with similar protocol stacks, the approach may be extended across different communication protocols.

#### TECHNICAL APPROACH

Our purpose is to define a feasible approach towards an efficient and reconfigurable controller that can be utilized by multiple protocols when implementing their logic PHY and DLL functions. This framework is designed to exploit the similarities amongst multiple serial-link protocols to achieve flexibility in implementation and reduction in power. The framework is divided in 3 groups- 1) configurable circuit, 2) programmable accelerator and 3) event processor, each with distinct functionalities and speeds of operation.

#### SUMMARY OF RESULTS

For a given functionality, our analysis indicates the necessity of introducing dedicated functional components as well as the possibility of sharing these across protocols. Based on similarity and throughput features, we define an entire architecture as shown in Figure 1, which contains UP-PHY and CRC modules implemented as configurable circuits, Framer and Deframer as programmable accelerators, and a microcontroller with event queue forming an event processor. An internal control bus is used by the processor to set-up configurable/programmable peripherals at initialization.

Group 1: The logic UP-PHY defines functions for processing bit streams including serialization/ deserialization, clock tolerance, encoding/decoding and scrambling/ descrambling.

Group 2: The framing/deframing module is a major part of DLL, which is responsible for constructing and extracting frames exchanged with logic PHY. So, data input and output rate is about 500M symbols per second (Sps) in USB 3.0 and PCIe 2.0 and 600M Sps in SATA 3.0.

Figure 1: Overview of the MMSLC architecture

Group 3: Our estimation of DLL in protocols also indicates the need of an embedded processor for event handling. These events will result in terrible context-switching overhead, as if using typical interrupt mechanism, when we take into account the high event frequency and large number of events. A complete context switching will cost almost 15 instruction cycles which occupies 60% of an average event handler. So we use a 2-phase event queuing mechanism to prevent processor from responding directly to an event.

The RTL model was synthesized in Synopsys using 90nm standard cell library to estimate the area of the circuit as well as to verify if the speed can meet the protocol's requirement. The results show that this architecture is capable of achieving the high-speed requirements of around 500MHz symbol rate for serial link protocols and realize area reduction over conventional link controllers running each protocol individually.

Furthermore, we are working towards broadening this work to achieve improved energy efficiency in MMSLC architecture.

**Keywords:** link controller, reconfigurable architecture, serial-link protocols, communication standards

### INDUSTRY INTERACTIONS

Texas Instruments

#### **MAJOR PAPERS/PATENTS**

[1] Lei Wang, Vishal Nawathe, Pawankumar Hegde et al., "Design of a Link-Controller architecture for Multiple Serial Link Protocols Energy-Efficient", IEEE SOCC 2010, Las Vegas, Nevada, USA, 27-29 September 2010.

### TASK ID# 1836.008, DIGITAL ASSISTED MM-WAVE CMOS CIRCUITS J. E. BREWER, UF, jebrewer@ufl.edu K.K.O, UTD, k.k.o@utdallas.edu

#### SIGNIFICANCE AND OBJECTIVES

To improve yield and shorten time to market of millimeter wave CMOS circuits, this task is Investigating the feasibility of incorporating digitally-controlled built-in tuning in millimeter wave circuits that mitigates the impact of process variations, modeling uncertainty of passive and active components.

#### **TECHNICAL APPROACH**

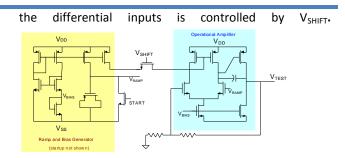

Detectors placed at the input and output of front-end amplifiers and mixer outputs of an RF transceiver can be used for measurements needed for tuning/calibrating the receiver and transmitter. The key challenges for realizing a digital assisted system operating at millimeter wave frequencies are (1) inexpensively injecting test signals, (2) incorporating tuning elements which do not add significant parasitics and degrade circuit performance, and (3) realizing high impedance broadband detectors with sufficient dynamic range. This effort will understand these challenges, and the limitations in the context of a 77-GHz reconfigurable low noise and power amplifiers fabricated in 45-nm CMOS.

#### SUMMARY OF RESULTS

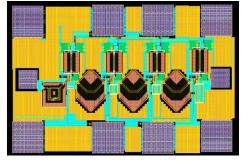

Test structures of tunable components including variable capacitors, inductors, and loads have been simulated and fabricated in 45-nm CMOS. The variable inductor has the maximum to minimum inductance ratio of ~1.8. A tunable 77-81 GHz low noise amplifier in Figure 1 has been fabricated. The four stage amplifier includes four tunable inductors that can tune the inter-stage matching. The center frequency gain can be tuned from 76 to 82 GHz, while that for the output matching can be tuned from 70-81 GHz. The amplifier achieves peak gain greater than 15 dB and minimum noise figure of ~8 dB.

Figure 1: 77-81 GHz tunable low noise amplifier.

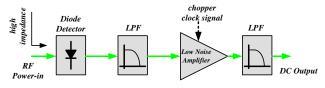

Test structures of diode detectors are also fabricated in the same process technology. The insertion of high impedance detector introduces around ~0.2-dB loss at 77 GHz. The detector as shown in Figure 2 also includes low pass filters and a chopper stabilized amplifier. The rms diode detector has dynamic range greater than 50 dB.

Figure 2: Diode detector and amplification circuits

The test structures and circuits are being characterized. A tunable power amplifier is being designed. Based on the measurements, the LNA and detector will be redesigned and integrated. Detectors will also be integrated into the power amplifier. Lastly, techniques for tuning a set of circuit parameters, including gain, linearity, and noise performance will be investigated.

**Keywords:** tunable, mm-wave, low noise amplifier, power amplifier.

#### INDUSTRY INTERACTIONS

Texas Instruments and Freescale

#### MAJOR PAPERS/PATENTS

[1] N. Zhang and K. K. O, "W-Band Pulsed Radar Receiver in Low Cost CMOS," Accepted to 2010 CICC.

[2] C. Mao et al., "Diodes in CMOS for Millimeter and Sub-Millimeter Wave Circuits," (Invited) 2010 Intl. Sym. on VLSI Tech., Systems and Applications, April, 2010, Hsinchu, Taiwan.

[3] C. Mao and K. K. O, "60-GHz Hybrid Transmit/Receive Switch Using p-n Diode and MOS Transistors," 2009 Symposium on VLSI Circuits, pp. 248-249, June 2009, Kyoto, Japan.

[4] N. Zhang et al., "CMOS Freq. Gen. Syst for W-Band Radar," 2009 Symp. on VLSI Circs., pp.126-127, June 2009, Kyoto, Japan.

[5] C. Mao et al., "65/130 GHz diode frequency doubler in 0.13-mm CMO," IEEE JSSC, vol. 44, no. 5, pp. 1531-1538, May 2009.

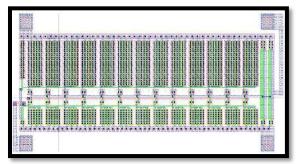

### TASK ID# 1836.011, POWER MINIMIZATION AND YIELD OPTIMIZATION IN DIGITAL ICS

CARL SECHEN, UNIVERSITY OF TEXAS-DALLAS, carl.sechen@utdallas.edu

#### SIGNIFICANCE AND OBJECTIVES

We address power minimization given a delay target in a synthesized digital logic block. To that end, we engineered a reduced cell library along with our optimal cell size selection algorithms that combine to achieve power reductions on large, contemporary industrial circuits.

#### **TECHNICAL APPROACH**

Tools have been produced that lower dynamic power by more than 35% on actual industrial digital circuits, and which lower leakage power by more than 70%, compared to state-of-the-art EDA tools. The tools select the optimal cell size and the optimal Vt among the options available in a cell library. The contents of a power-optimal physical cell library have been identified, and the contents of a (rather different) power-optimal synthesis cell library have been determined. The physical cell library (only 8 gate types) is dramatically smaller than those currently used in industry, while achieving much lower dynamic and leakage power for industrial circuits.

#### SUMMARY OF RESULTS

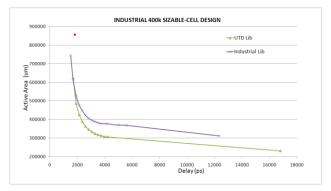

We demonstrated that optimal cell size selection, including optimized threshold voltage selection, along with a new discrete cell size mapping algorithm enable substantial reductions in total power and leakage power for industrial digital blocks compared to leading synthesis tools. We were further able to engineer a highly power efficient cell library composed of far fewer cells than is common in commercial libraries, including functional content, drive strengths and beta ratios. The size selection algorithms in conjunction with the reduced library size enable this combination of library and tools to efficiently handle the large layout partitions used in contemporary ASICs, which typically have 500k to 2 million sizeable cells.

Our approach includes nearly globally optimal cell size selection from options in a standard cell library, as well as nearly optimal Vt selection among options available in the cell library. We have also developed precise static timing analysis, accurate to spice and more accurate than the leading commercial static timing analyzer. Our tools handle commercial multi-million gate designs today. We have also developed the most power efficient standard cell library that consists of only 8 combinational gate types in addition to flip-flops.

Figure 1: A typical result is shown above for a 2010 multimillion gate industrial design in 40nm. The red dot is the best result produced by the leading commercial synthesis tool. Active area, immediately proportional to dynamic power, was reduced by more than 2X (for the same delay) and the UTD optimal cell library (using only 8 types of gates) reduced dynamic power by 20% over a leading commercial cell library. Leakage power was reduced by 80% versus the leading commercial synthesis tool for the same delay.

**Keywords:** Gate sizing, gate size selection, threshold voltage selection, power minimization, optimal cell libraries.

#### INDUSTRY INTERACTIONS

**Texas Instruments**

#### MAJOR PAPERS/PATENTS

[1] M. Rahman, H. Tennakoon, and C. Sechen, "Near Optimal Power Efficiency Through Gate Sizing", Proc. Austin Conf. on Integrated Circuits and Systems (ACISC), Oct. 26-27, 2009, Austin, TX.

[2] R. Afonso, M. Rahman, H. Tennakoon, and C. Sechen, "Power Efficient Standard Cell Library Design", Proc. IEEE Dallas Circuits and Systems Society Workshop, Oct. 4-5, 2009, Dallas, TX.

[3] H. Tennakoon and C. Sechen, "Non-convex Gate Delay Modeling and Delay Optimization," IEEE Trans. on Computer-Aided Design, Vol. 27, No. 9, September 2008, pp. 1583-1594.

[4] Several patents are planned for late 2010.

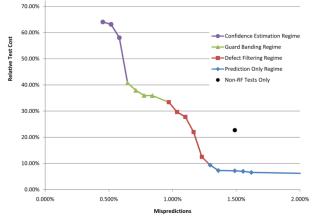

### TASK ID# 1836.012, STRUCTURAL FAULT MODELING, TESTING, AND DEFECT LEVEL ESTIMATION FOR ANALOG/RF CIRCUITS SULE OZEV, ARIZONA STATE UNIVERSITY sule.ozev@asu.edu

#### SIGNIFICANCE AND OBJECTIVES

In order to provide an alternative to specification-based testing, various test and built-in-test techniques have been proposed. However, there is a lack of a mechanism to predict the test quality This project aims at (a) fault modeling, (b) test development based on these models, (c) estimating the overall test quality.

#### **TECHNICAL APPROACH**

Fault models are based on continuous behavior of defects. A statistical framework is developed to evaluate and define tests based on the continuous fault models together with process variations. The process variation model includes both within-die and die-to-die components. For test development, both specifications and other parameters are considered. These tests can be evaluated with respect to their fault coverage. Based on statistical analysis, each test has a certain probability of detecting deviations in a given parameter. By collecting this statistical information over many parameters, an overall fault coverage metric can be calculated and used to select tests.

#### SUMMARY OF RESULTS

First, parametrizable defect models have been generated using 3D electromagnetic simulations. Various defect sizes have been simulated for known defect types, such as missing vias, pinhole defects, etc. A library of faults based on defect size has been generated. Probability of a defect decreases with its size. Using this information, and the defect simulation based on size, each circuit can be evaluated using transistor-level simulations.

Two issues make these simulations quite challenging. First, with process variations, each fault simulation becomes a statistical simulation, making it computationally very expensive. Second, such fault simulation also requires the knowledge of absolute defect probability, which is generally not available.

We aim at resolving these issues with novel approaches. Inductive fault analysis tries to obtain defect probabilities. However, accuracy is typically limited. We take a unique approach where we decouple the inductive fault analysis from the absolute defect probability. Inductive fault analysis is used to obtain a relative probability distribution for each fault. For example, a break in a thick metal line is much less likely than a break in a thin metal line. Then, we use initial characterization data, in conjunction with outlier analysis to determine a baseline defectivity level. Combined with relative fault probabilities, this defectivity level is used to approximate the defect probability.

In order to solve the tractability problem, we develop a hierarchical fault simulation methodology. First, we attack the problem of high number of simulations by classifying fault responses with respect to how far they lay from the specification or pass/fail limits. This first cut eliminates a large number of faults from more extensive simulations as their responses are immediately classifiable as pass or fail. For the remaining faults, we take advantage of the layered nature of process variations. For die-to-die variations, we have only a small number of parameters, and can afford to use enumerative techniques, such as Taguchi's method. For within-die variations, the number of parameters is large. However, variations are smaller. We conduct a more detailed characterization of these faults. Table I shows the speed-up we can achieve when compared with Monte-Carlo simulations alone for an LNA circuit.

TABLE I: Speed-up in fault simulations when compared with Monte-Carlo analysis

| # Simulations |          | DP | DPPM Error |  |

|---------------|----------|----|------------|--|

| МС            | Proposed | мс | Proposed   |  |

| 100K          | 3К       | 0  | 0.4        |  |

**Keywords:** fault modeling, analog testing, test development, fault simulation, test quality

#### INDUSTRY INTERACTIONS

Texas Instruments, Intel, IBM, Freescale

#### **MAJOR PAPERS/PATENTS**

"Accurate Multi-Specification DPPM Estimation Using Layered Sampling Based Simulation", ISQED 2010.

"Defect-Based Test Optimization for Analog/RF Circuits for Near-Zero DPPM Applications", ICCD 2009.

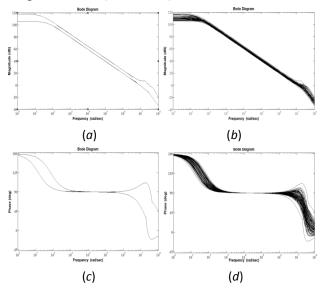

# TASK ID# 1836.013, WIDEBAND RECEIVER ARCHITECTURES IN DIGITAL DEEP SUBMICRON CMOS

SEBASTIAN HOYOS, TEXAS A&M UNIVERSITY, COLLEGE STATION, <u>hoyos@ece.tamu.edu</u> JOSE SILVA-MARTINEZ, TEXAS A&M UNIVERSITY, COLLEGE STATION

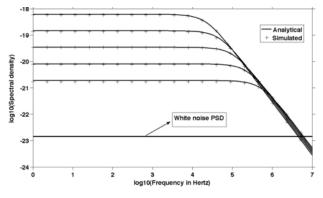

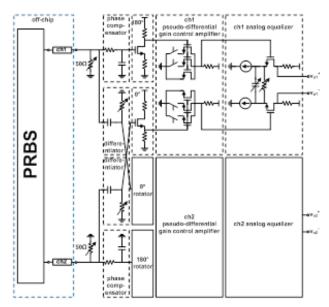

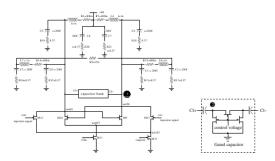

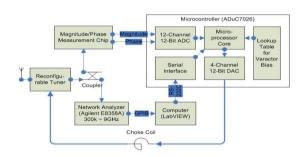

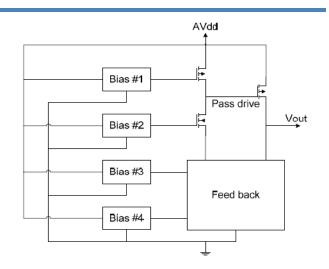

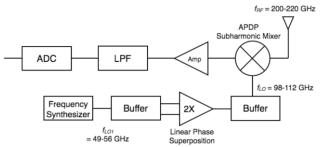

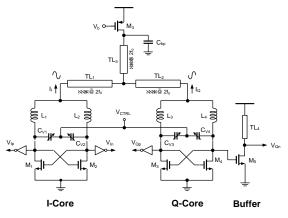

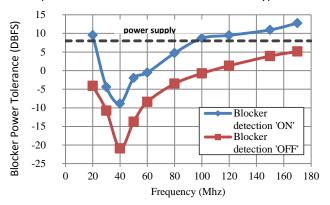

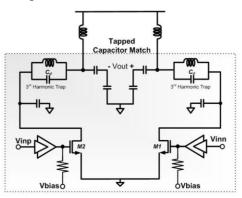

#### SIGNIFICANCE AND OBJECTIVES